Publication list

A. 書籍 Books

- 兼本大輔を含む多数,生体センシング技術の開発とヘルスケア、遠隔診断への応用, 技術情報協会, 2024年4月

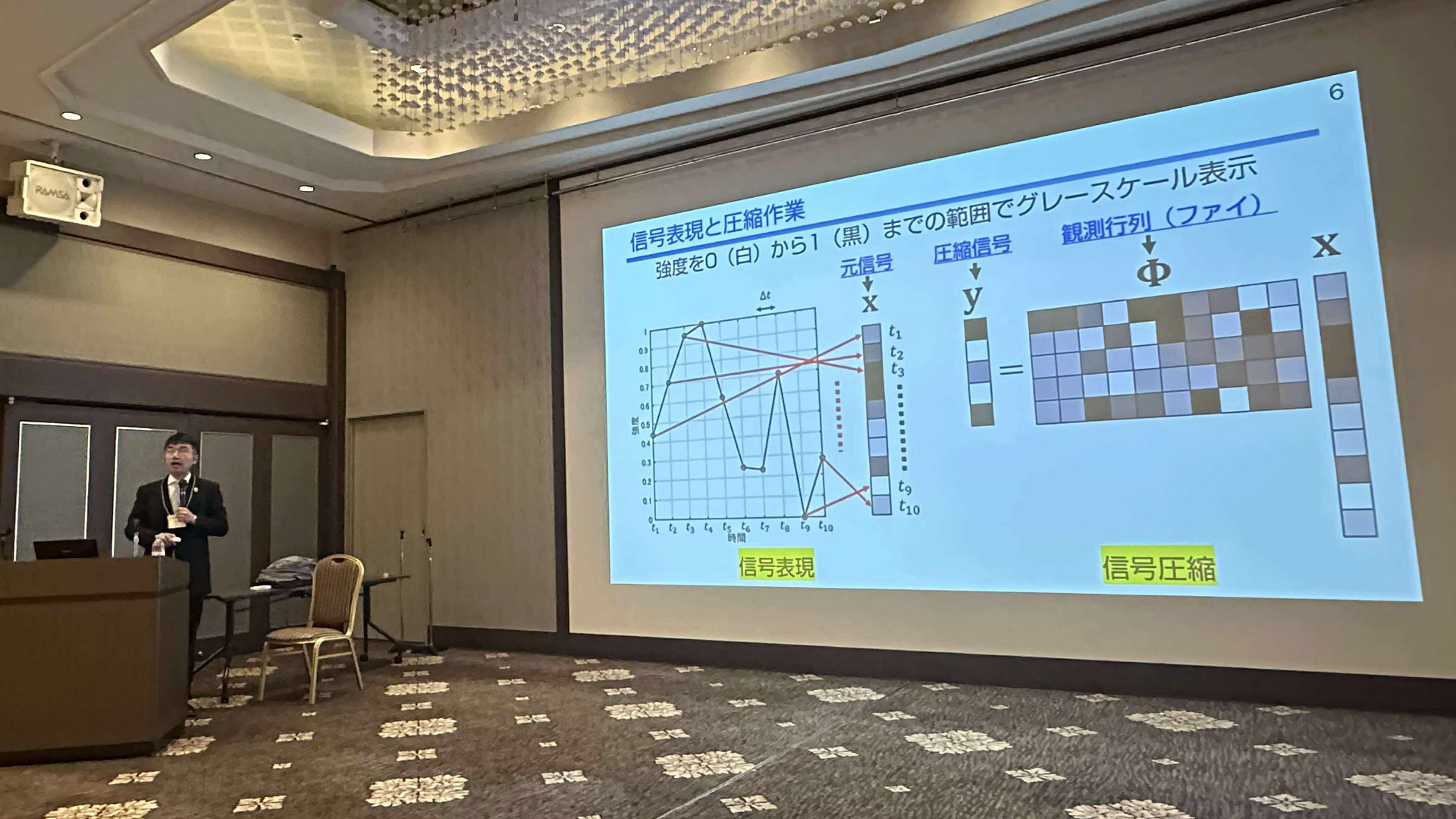

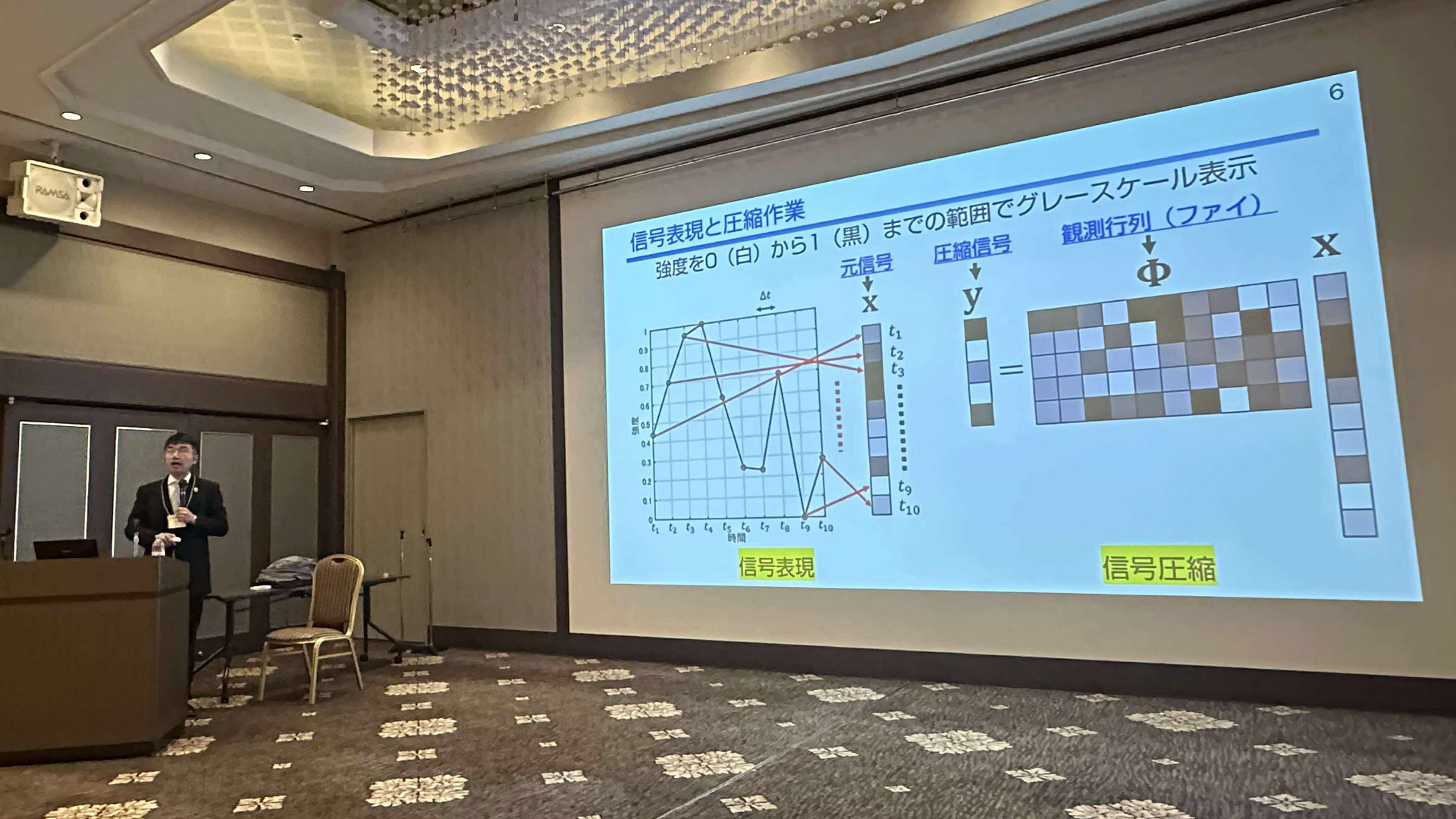

兼本執筆箇所「圧縮センシングを活用した低消費電力生体信号計測システム」

B. 原著論文(査読有) Journal Papers (refereed)

- Hikaru Sebe, Tomoo Okumura, Shintaro Sumi, Daisuke Kanemoto, P. -H. Chen, and Tetsuya Hirose,“30-mV supply ring oscillator employing recursive-stacking body-bias inverters for extremely-low-voltage energy harvesting,” IEICE Trans. Electron., vol. E109.C, no. 7, pp. - , 2026. (in press)

- Shintaro Sumi, Daisuke Kanemoto, and Tetsuya Hirose,“Sub-50-mV extremely low-voltage flip-flop circuit consisting of recursive stacking body-bias CMOS logic gates,” IEICE Trans. Electron., vol. E109.C, no. 7, pp. - , 2026. (in press)

- 松本 香, 黒木修隆, 沼 昌宏, 毎田 修, 兼本大輔, 廣瀬哲也,“光エネルギーハーベスティング応用に向けたオンチップフォトダイオードと昇圧回路の構成法比較評価,” 電子情報通信学会論文誌C, Vol. J109-C, No. 1, pp. , 2026. (採録決定)

- Jingbo Li, Yosuke Mizuno, Hikaru Sebe, Shintaro Sumi, Daisuke Kanemoto, and Tetsuya Hirose,“Ultra-low quiescent current off-chip capacitor-less low-dropout linear regulator with enhanced load-transient response for low-power IoT devices,” Jpn. J. Appl. Phys. 64, , 2025.

- Hikaru Sebe, Daisuke Kanemoto, and Tetsuya Hirose, “Sub-60-mV Charge Pump and its Driver Circuit for Extremely Low-Voltage Thermoelectric Energy Harvesting,” IEICE Trans. Electron., vol. E107-C, no. 10, pp. 400-407, Apr. 2024.

- Yoshinori Itotagawa, Koma Atsumi, Hikaru Sebe, Daisuke Kanemoto, and Tetsuya Hirose, “Programmable Differential Bandgap Reference Circuit for Ultra-Low-Power CMOS LSIs,” IEICE Trans. Electron., vol. E107-C, no. 10, pp. 392-399, Apr. 2024.

- Shintaro Sumi, Hikaru Sebe, Daisuke Kanemoto, and Tetsuya Hirose, “Sub-50-mV power supply, recursive stacking body bias NAND gate for extremely low-voltage CMOS LSI,” Jpn. J. Appl. Phys. ,63, 03SP87, 2024.

- Kenji Mii, Daisuke Kanemoto, and Tetsuya Hirose, “0.36μW/channel Capacitively-coupled Chopper Instrumentation Amplifier in EEG Recording Wearable Devices for Compressed Sensing Framework,” Jpn. J. Appl. Phys. 63, 03SP54, 2024.

- Yosuke Mizuno, Hikaru Sebe, Daisuke Kanemoto, and Tetsuya Hirose, “Ultra-low power low-dropout linear regulator with a load current tracking bias current generator for loT devices,” Jpn. J. Appl. Phys. 63, 02SP96, 2024.

- Kenji Mii, Daisuke Kanemoto, and Tetsuya Hirose, “Low Quiescent Current LDO with FVF-Based PSRR Enhanced Circuit for EEG Recording Wearable Devices,” Jpn. J. Appl. Phys. 63, 03SP33, 2024.

- Ryo Matsuzuka, Shuto Kanzaki, Kaori Matsumoto, Nobutaka Kuroki, Masahiro Numa, Daisuke Kanemoto, and Tetsuya Hirose, “Switched-capacitor voltage buck converter with variable step-down and switching frequency controllers for low-power and high-efficiency IoT devices,” Jpn. J. Appl. Phys. 62, SC1082, 2023.

- Kaori Matsumoto, Ryuki Ikeda, Hikaru Sebe, Nobutaka Kuroki, Masahiro Numa, Daisuke Kanemoto, and Tetsuya Hirose, “Fully-integrated switched-capacitor voltage boost converter with digital maximum power point tracking for low-voltage energy harvesting,” Jpn. J. Appl. Phys. 62, SC1071, 2023.

- Yuki Okabe, Daisuke Kanemoto, Osamu Maida, and Tetsuya Hirose, “Compressed Sensing EEG Measurement Technique with Normally Distributed Sampling Series,” IEICE Trans. Fundamentals, vol.E105-A, no.10,pp.1429-1433,Oct. 2022.

- Yuuki Harada, Daisuke Kanemoto, Takahiro Inoue, Osamu Maida, and Tetsuya Hirose, “Image Quality Improvement for Capsule Endoscopy Based on Compressed Sensing with K-SVD Dictionary Learning,” IEICE Trans. Fundamentals, vol. E105-A, no.4, pp. 743-747, Apr. 2022.

- Osamu Maida, Daisuke Kanemoto, and Tetsuya Hirose, “Characterization of deep interface states in SiO2/B-doped diamond using the transient photocapacitance method,” Thin Solid Films, Nov. 2021, 139026.

- Masaya Nishi, Kaori Matsumoto, Nobutaka Kuroki, Masahiro Numa, Hikaru Sebe, Ryo Matsuzuka, Osamu Maida, Daisuke Kanemoto, and Tetsuya Hirose, “A 35-mV supply ring oscillator consisting of stacked body bias Inverters for extremely low-voltage LSIs,” IEICE Electron. Express, vol. 18, no 6, pp.1-6, 2021.

- Daisuke Kanemoto, Jonathon Spaulding, and Boris Murmann, “Single-chip mixer-based subarray beamformer for sub-Nyquist sampling in ultrasound imaging,” Jpn. J. Appl. Phys. 60, SBBL08, 2021.

- Hikaru Sebe, Kaori Matsumoto, Ryo Matsuzuka, Osamu Maida, Daisuke Kanemoto, and Tetsuya Hirose, “A self-bias NAND gate and its application to non-overlapping clock generator for extremely low-voltage CMOS LSIs,” Jpn. J. Appl. Phys. 60, SBBL06, 2021.

- Kotaro Nagai, Daisuke Kanemoto, and Makoto Ohki, “Applying K-SVD Dictionary Learning for EEG Compressed Sensing Framework with Outlier Detection and Independent Component Analysis,” IEICE Trans. Fundamentals, vol. E104-A, no. 09, pp. 1375-1378, Sep. 2021.

- Daisuke Kanemoto, Shun Katsumata, Masao Aihara, and Makoto Ohki, “Compressed Sensing Framework Applying Independent Component Analysis after Undersampling for Reconstructing Electroencephalogram Signals,” IEICE Trans. Fundamentals, vol. E103-A, no. 12, pp. 1647-1654, Dec. 2020.

- Tomoya Kageyama, Daisuke Kanemoto, Oruto Endo, Makoto Ohki, and Osamu Muta, “Effect of Hysteresis-based Simple Negative Feedback A/D Conversion on Channel Estimation for Single Carrier Modulation,” IEICE Commun. Express, vol. 9, issue 7, pp. 274-281, Jul. 2020.

- Kaori Matsumoto, Hiroki Asano, Yuichiro Nakazawa, Nobutaka Kuroki, Masahiro Numa, Osamu Maida, Daisuke Kanemoto, and Tetsuya Hirose, “An 11.8 nA ultra-low power active diode using a hysteresis common gate comparator for low-power energy harvesting systems,” IEICE Electron. Express, vol. 17, issue 11, pp. 1-6, Jun. 2020.

- Shingo Nakamura, Daisuke Kanemoto, Tomoki Sadakiyo, and Haruichi Kanaya, “High-efficiency CMOS push-pull power amplifier with multilayer center-tapped transformer,” IEEJ Trans. Electr. Electron. Eng., vol. 11, no. 3, pp. 384-386, May 2016.

- 佐藤隆英, 遠藤真輝,兼本大輔, “独立成分分析を用いた胎児の心電信号測定に適する小面積・低消費電力多チャネル増幅回路,” 電気学会論文誌C, vol. 136, no. 1 pp. 50-59, Jan. 2016.

- 佐藤隆英, 一見貴文,兼本大輔,“チャージポンプ回路の制御信号のデューティ比による出力電圧の制御と2ステップ充電技術を用いたチャージポンプ回路への応用,” 電気学会論文誌C, vol. 135, no. 1, pp. 26-34, Jan. 2015.

- Koji Fujita, Daisuke Kanemoto, Kuniaki Yoshitomi, Keiji Yoshida, and Haruichi Kanaya, “Multiband (920 MHz/2.4 GHz/3.5 GHz/5 GHz) Planar Antenna on Flexible Substrate,” Microw. Opt. Technol. Lett., vol 56, issue 11, pp. 2526-2530, Nov. 2014.

- Toru Okazaki, Daisuke Kanemoto, Ramesh Pokharel, Keiji Yoshida, and Haruichi Kanaya, “A Design Methodology for SAR ADC Optimal Redundancy Bit,” IEICE Electron. Express, vol. 11, no. 10, pp. 1-6, Apr. 2014.

- Tomoya Ijiguchi, Daisuke Kanemoto, Kuniaki Yoshitomi, Keiji Yoshida, Akira Ishikawa, Shugo Fukagawa, Joriyuki Kodama, Akihiro Tahira, and Haruichi Kanaya, “Circularly Polarized One-Sided Directional Slot Antenna With Reflector Metal for 5.8-GHz DSRC Operations,” IEEE Antennas Wirel. Propag. Lett., vol. 13, pp. 778-781, Apr. 2014.

- Daisuke Kanemoto, Keigo Oshiro, Keiji Yoshida, Ramesh Pokharel, and Haruichi Kanaya, “A 10-bit 50MS/s 350μW Small Die Area Capacitive Digital-to-Analog Converter for Bluetooth Applications,” IEEJ Trans. Electr. Electron. Eng., vol. 134, no. 2, pp. 328-329, Feb. 2014.

- 橋村亮介, アウィナシアナンド, ポカレルラメシュ, 兼本大輔, 金谷晴一, 吉田啓二, “負性抵抗を利用した低位相雑音,広周波数可変範囲を持つ4位相出力15ビットディジタル制御リング型発振器の開発,” 電子情報通信学会論文誌 A, vol. J96-A, no. 6, pp. 370-376, 2013年6月.

- Yuki Yamashita, Daisuke Kanemoto, Haruichi Kanaya, Ramesh K. Pokharel, and Keiji Yoshida, “A self-biasing class-E power amplifier for 5-GHz constant envelope modulation system,” IEICE Electron. Express, vol. 10, no. 8, pp. 1-7, Apr. 2013.

- Haruichi Kanaya, Shoichiro Tsukamoto, Takuya Hirabaru, Daisuke Kanemoto, Ramesh Pokharel, and Keiji Yoshida, “Energy Harvesting Circuit on a One-sided Directional Flexible Antenna,” IEEE Microw. Wirel. Compon. Lett., vol. 23, no. 3, pp. 164-166 Mar. 2013.

- Daisuke Kanemoto, Toru Ido, and Kenji Taniguchi, “A High Dynamic Range and Low Power Consumption Audio Delta-Sigma Modulator with Opamp Sharing Technique among Three Integrators,” IEICE Trans. Electron., vol. E95-C, no. 8, pp. 1427-1433, Aug. 2012.

- Daisuke Kanemoto, Yu Tamura, Bogoda Indika, Toshimasa Matsuoka, and Kenji Taniguchi, “A Novel RC Time Constant Tuning Technique utilizing Programmable Current Sources for Continuous-time Delta-Sigma Modulators,” IEICE Electron. Express, vol. 9, no. 6, pp. 572-579, Mar. 2012.

- Kazuya Hokazono, Daisuke Kanemoto, Haruichi Kanaya, Ramesh Pokharel, and Keiji Yoshida, “A Novel High-Precision DAC utilizing Tribonacci Series,” IEICE Electron. Express, vol. 9, no. 6, pp. 515-521, Mar. 2012.

- 田村 悠, 兼本大輔, 松岡俊匡, 谷口研二, “デルタシグマ型ディジタル/アナログ変換器のための循環型部分的DWA手法,” 電子情報通信学会論文誌C, vol. J95-C, no. 1, pp. 9-17, 2012年1月.

- Ghazal Fahmy, Daisuke Kanemoto, Haruichi Kanaya, Pamesh Pokharel, Keiji Yoshida, and Awinash Anand, “A third order Delta-Sigma Modulator employing Shared Opamp technique for WCDMA on 0.18um CMOS,” IEICE Electron. Express, vol. 8, no. 15, pp. 1204-1209, Aug. 2011.

- Bogoda Indika, Daisuke Kanemoto, and Kenji Taniguchi, “A novel 100ppm/oC current reference for ultra low-power subthreshold applications,” IEICE Electron. Express, vol. 8, no. 3, pp. 168-174, Feb. 2011.

- Daisuke Kanemoto, Toru Ido, and Kenji Taniguchi, “A novel third order Delta Sigma Modulator with one opamp shared among three integrator stages,” IEICE Electron. Express, vol. 5, no. 24, pp. 1088-1092, Dec. 2008.

- 兼本大輔, 谷口研二, “アクティブRC積分器のフィードフォワード充電法,” 電子情報通信学会論文誌C, vol. J89-C, no. 10, pp. 641-644, 2006年10月.

C. 国際会議論文(査読有) International Conferences (refereed)

- So Iwanari, Kira Tanigami, Hikaru Sebe, Daisuke Kanemoto, and Tetsuya Hirose,"Self-powered bias-flip rectifier with on-chip flip switch timing controller for piezoelectric energy harvesting," in Ext. Abstr. Solid State Devices and Materials (SSDM), Sep. 2025,.

- Takuma Matsumori, Hikaru Sebe, Daisuke Kanemoto, and Tetsuya Hirose,"CMOS readout circuit with delay and offset voltage compensation for membrane-type surface-stress sensors," in Ext. Abstr. Solid State Devices and Materials (SSDM), Sep. 2025,.

- Yuma Yasuda, Shintaro Sumi, Daisuke Kanemoto, and Tetsuya Hirose,"Comparative study of extremely low-voltage recursive stacking feedforward/Feedback Body Bias Inverters," in Ext. Abstr. Solid State Devices and Materials (SSDM), Sep. 2025,.

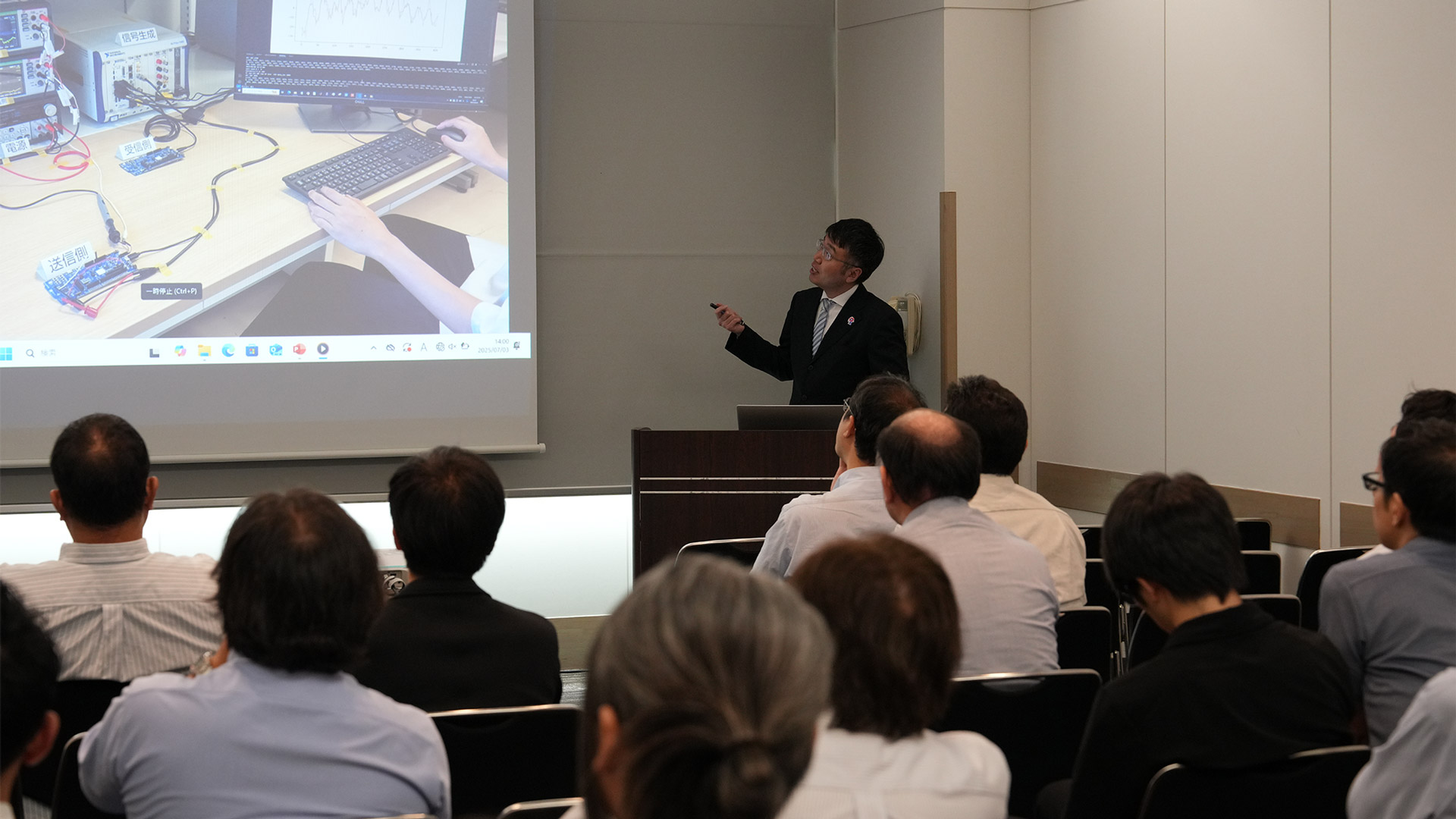

- Daisuke Kanemoto, Eichi Takimoto, and Tetsuya Hirose, “Development of Low-Power and High-Accuracy Wireless EEG Transmission System Using Compressed Sensing with an EEG Basis,” in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2025. pp. 1-5 .

- Kenji Mii, Daisuke Kanemoto, and Tetsuya Hirose, “Low-Power and Low-Noise Amplifier with Intermittent Operation for Compressed Sensing in EEG Measurement Systems,” in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2025. pp.1-5.

- Shintaro Sumi, Daisuke Kanemoto, and Tetsuya Hirose, “Sub-50-mV Static Flip-Flop Consisting of Recursive Stacking Body-Bias Logic Gates for Extremely Low-Voltage LSIs,” in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2025. pp.1-5.

- Tomoya Yamamoto, Daisuke Kanemoto, and Tetsuya Hirose,"Noise-Masking Cryptosystem Using Watermark and Chain Generation for EEG Measurement with Compressed Sensing," in Proc. IEEE Int. Conf. Consum. Electron. (ICCE), Jan. 2025, pp.1-6.

- Riku Matsubara, Daisuke Kanemoto, and Tetsuya Hirose,"Design Guidelines for Noise in a Low-Noise Amplifier Using EEG Signals as a Basis Matrix in Compressed Sensing System," in Proc. IEEE Int. Conf. Consum. Electron. (ICCE), Jan. 2025, pp.1-5.

- Kenji Mii, Daisuke Kanemoto, and Tetsuya Hirose, “Low quiescent current LDO with FBPEC to improve PSRR specific frequency band for wearable EEG recording devices,” in Proc. 30th Asia and South Pacific Design Automation Conference (ASP-DAC 2025), Jan. 2025, pp. 356-359 .

- Kenji Mii, Daisuke Kanemoto, and Tetsuya Hirose, “Ultra Low-power Capacitively-coupled Chopper Amplifier Focusing on the Sparsity of Compressed Sensing for EEG Recording,” in Proc. 30th Asia and South Pacific Design Automation Conference (ASP-DAC 2025), Jan. 2025, pp. 368-371.

- Jingbo Li, Yosuke Mizuno, Hikaru Sebe, Shintaro Sumi, Daisuke Kanemoto, and Tetsuya Hirose,"Ultra-low quiescent current capacitor-less low-dropout linear regulator with enhanced load-transient response," in Ext. Abstr. Solid State Devices and Materials (SSDM), Sep. 2024, pp.1-4.

- Riku Matsubara, Daisuke Kanemoto, and Tetsuya Hirose, “Reducing Power Consumption in LNA by Utilizing EEG Signals as Basis Matrix in Compressed Sensing,” in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2024. pp.1-5.

- Takuya Miyata, Daisuke Kanemoto, and Tetsuya Hirose,"Utilizing Previously Acquired BSBL Algorithm Parameters in the Compressed Sensing Framework for EEG Measurements," in Proc. IEEE Int. Conf. Consum. Electron. (ICCE), Jan. 2024, pp.1-5.

- Ryota Tsunaga, Daisuke Kanemoto, and Tetsuya Hirose,"Noise-Masking Cryptosystem Using Watermark and Chain Generation for EEG Measurement with Compressed Sensing," in Proc. IEEE Int. Conf. Consum. Electron. (ICCE), Jan. 2024, pp.1-6.

- Kenji Mii, Daisuke Kanemoto, and Tetsuya Hirose,"Low Quiescent Current Capacitively-coupled Chopper Instrumentation Amplifier in EEG Recording Wearable Devices for Compressed Sensing Framework," in Ext. Abstr. Solid State Devices and Materials (SSDM), Sep. 2023, pp.917-918.

- Kenji Mii, Daisuke Kanemoto, and Tetsuya Hirose,"Low Quiescent Current LDO with FVF-Based PSRR Enhanced Circuit for EEG Recording Wearable Devices," in Ext. Abstr. Solid State Devices and Materials (SSDM), Sep. 2023, pp.411-412.

- Shintaro Sumi, Hikaru Sebe, Daisuke Kanemoto, and Tetsuya Hirose,"A sub-50-mV supply, recursive stacking body bias NAND gate for extremely low-voltage energy harvesting," in Ext. Abstr. Solid State Devices and Materials (SSDM), Sep. 2023, pp.913-914.

- Yosuke Mizuno, Hikaru Sebe, Daisuke Kanemoto, and Tetsuya Hirose,"An Ultra-Low Power Low-Dropout Regulator with a Load Current Tracking Bias Current Generator," in Ext. Abstr. Solid State Devices and Materials (SSDM), Sep. 2023, pp.911-912.

- Hikaru Sebe, Tomoo Okumura, Shintaro Sumi, Daisuke Kanemoto, P. -H. Chen, and Tetsuya Hirose, “A sub-30-mV supply, Fully Integrated Ring Oscillator Consisting of Recursive Stacking Body Bias Inverters for Extremely low-Voltage Energy Harvesting,” in Proc. Eur. Solid-State Circuits Conf. (ESSCIRC), Sep. 2023, pp.325-328.

- Daisuke Kanemoto, and Tetsuya Hirose, “EEG Measurements with Compressed Sensing Utilizing EEG Signals As the Basis Matrix,” in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2023. pp.1-5.

- Takuya Miyata, Daisuke Kanemoto, and Tetsuya Hirose, “Random Undersampling Wireless EEG Measurement Device Using a Small TEG,” in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2023. pp.1-5.

- Yoshinori Itotagawa, Koma Atsumi, Hikaru Sebe, Daisuke Kanemoto, and Tetsuya Hirose, “A Programmable Differential Bandgap Reference for Ultra-Low-Power IoT Edge Node Devices,” in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2023. pp.1-5.

- Ryo Matsuzuka, Shuto Kanzaki, Kaori Matsumoto, Nobutaka Kuroki, Masahiro Numa, Daisuke Kanemoto, and Tetsuya Hirose,"Fully Integrated Switched-Capacitor Buck Converter with Variable Ratio and Frequency Controllers for Ultra-Low Power LSI Systems," in Ext. Abstr. Solid State Devices and Materials (SSDM), Sep. 2022, pp.798-799.

- Kaori Matsumoto, Ryuki Ikeda, Hikaru Sebe, Nobutaka Kuroki, Masahiro Numa, Daisuke Kanemoto, and Tetsuya Hirose,"Switched-Capacitor Voltage Boost Converter with Digital Maximum Power Point Tracking for Low-Voltage Energy Harvesting," in Ext. Abstr. Solid State Devices and Materials (SSDM), Sep. 2022, pp.800-801.

- Hikaru Sebe, Daisuke Kanemoto, and Tetsuya Hirose, “Sub-50-mV Charge Pump and its Driver for Extremely Low-Voltage Thermal Energy Harvesting”, in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2022. pp.1-5.

- Hikaru Sebe, Kaori Matsumoto, Ryo Matsuzuka, Osamu Maida, Daisuke Kanemoto, and Tetsuya Hirose,"A Self-Bias NAND Gate and its Application to Non-Overlapping Clock Generator for Extremely Low-Voltage CMOS LSIs," in Ext. Abstr. Solid State Devices and Materials (SSDM), Sep. 2020, pp. 65-66.

- Daisuke Kanemoto, Jonathon Spaulding, and Boris Murmann, “One Chip Mixer-Based Subarray Beamformer for Ultrasound Imaging with Sub-Nyquist Rate ADC,” in Ext. Abstr. Solid State Devices and Materials (SSDM), Sep. 2020, pp. 785-786.

- Masaya Nishi, Kaori Matsumoto, Nobutaka Kuroki, Masahiro Numa, Hikaru Sebe, Ryo Matsuzuka, Osamu Maida, Daisuke Kanemoto, and Tetsuya Hirose, “A 34-mV startup ring oscillator using stacked body bias inverters for extremely low-voltage thermoelectric energy harvesting,” in Proc. 18th IEEE Int. New Circuits Syst. Conf. (NEWCAS), Jun. 2020, pp. 38-41.

- Masaya Nishi, Yuichiro Nakazawa, Kaori Matsumoto, Nobutaka Kuroki, Masahiro Numa, Ryo Matsuzuka, Osamu Maida, Daisuke Kanemoto, and Tetsuya Hirose, “Sub-0.1V Input, Low-Voltage CMOS Driver Circuit for Multi-Stage Switched Capacitor Voltage Boost Converter,” in Proc. 26th IEEE Int. Conf. Electron. Circuits Syst. (ICECS), Nov. 2019, pp. 1-4.

- Shun Katsumata, Daisuke Kanemoto, and Makoto Ohki, “Applying Outlier Detection and Independent Component Analysis for Compressed Sensing EEG Measurement Framework,” in Proc. IEEE Biomed. Circuits Syst. Conf. (BioCAS), Oct. 2019, pp. 1-4.

- Daisuke Kanemoto, Shun Katsumata, Masao Aihara, and Makoto Ohki, “Framework of Applying Independent Component Analysis After Compressed Sensing for Electroencephalogram Signals,” in Proc. IEEE Biomed. Circuits Syst. Conf. (BioCAS), Oct. 2018, pp. 145-148.

- Oruto Endo, Daisuke Kanemoto, and Makoto Ohki, “System Level Design of Continuous-time Delta Sigma Modulator Considering Relationship between Opamp GBWP and Quantizer Gain,” in Proc. The 32nd International Technical Conference on Circuits/Systems, Computers and Communications (ITC-CSCC), Jul. 2017, pp. 1-2.

- Daisuke Kanemoto, and Makoto Ohki, “A CT Delta-Sigma Modulator Design Technique with Equivalent Gain of Multi-bit ADC Having Random Offset Voltage due to Device Mismatch,” in Proc. IEEE/ACM Workshop on Variability Modeling and Characterization (VMC), Nov. 2015, pp. 1-2.

- Yuki Kawamata, Daisuke Kanemoto, and Makoto Ohki, “A Chopper Amplifier Utilizing Optimized Chopping Frequency for EEG Signal Processing Devices,” in Proc. IEEE Symp. Low-Power High-Speed Chips (COOL CHIPS), Apr. 2015, Poster 13.

- Daisuke Kanemoto, Naoki Fukasawa, Takahide Sato, and Makoto Ohki, “A 3rd Order Delta-Sigma Modulator Utilizing Equivalent Gain of Internal Multi-bit ADC,” in Proc. IEEE Symp. Low-Power High-Speed Chips (COOL CHIPS), Apr. 2015, Poster18.

- Osamu Muta, Daisuke Kanemoto, Syota Fukushige, and Hiroshi Furukawa, “Effect of Linearity Enhancement in A/D Conversion for Single Carrier Transmission Systems,” in Proc. IEEE 81st Vehicular Technology Conference (VTC2015-Spring), May 2015, pp. 1-5.

- Shota Fukushige, Osamu Muta, Daisuke Kanemoto, and Hiroshi Furukawa, “Performance of Single Carrier Transmission System Using Nonlinearity Mitigated A/D Converter,” in Proc. The Third International Japan-Egypt Conference on Electronics, Communications and Computers (JEC-ECC 2015), Mar. 2015, pp. 1-3.

- Daisuke Kanemoto, Keigo Oshiro, Keiji Yoshida, and Haruichi Kanaya, “A Tri-level 50MS/s 10-bit Capacitive-DAC for Bluetooth Applications,” in Proc. 20th Asia and South Pacific Design Automation Conference (ASP-DAC 2015), Jan. 2015, pp. 34-35.

- Takahide Sato, Takeshi Nagata, and Daisuke Kanemoto, “High Frquency Ring Oscillator Using Capacitor Based Level Shift Circuits,” in Proc. IEEE Asia Pac. Conf. Circuits Syst. (APCCAS), Nov. 2014, pp. 149-152.

- Shingo Nakamura, Ramesh Pokharel, Keiji Yoshida, Haruichi Kanaya, and Daisuke Kanemoto, “High Efficient Impedance Matching Circuit of Power Amplifier Combined with Antenna,” in Proc. Asia Pacific Conference on Wireless and Mobile 2014, Aug. 2014, pp. 84-87.

- Daisuke Kanemoto, Osamu Muta, Hiroshi Furukawa, Takahide Sato, and Makoto Ohki, “Linearity Enhancement Technique for one bit A/D converter in wireless communication devices,” in Proc. IEEE Int. Symp. Consum. Electron. (ISCE), Jun. 2014, pp. 199-200.

- Hirotaka Nonaka, Yoichi Ishizuka, Kenji Mii, Fumiaki Takenami, and Daisuke Kanemoto, “Sub-Microsecond Response Digital Controller for POL,” in Proc. International Power Electronics Conference -ECCE ASIA- IPEC-Hiroshima 2014, May 2014, pp. 2737-2743.

- Daisuke Kanemoto, Osamu Muta, Hiroshi Furukawa, Takahide Sato, and Makoto Ohki, “A Novel Idea of One Bit Resolution ADC for Small Analog Hardware Wireless Receivers,” in Proc. IEEE Symp. Low-Power High-Speed Chips (COOL CHIPS), Apr. 2014, Poster 11. Best Poster Award

- Yoichi Ishizuka, Kenji Mii, Fumiaki Takenami, and Daisuke Kanemoto, “1MHz Switching Frequency POL with a Fast Response Digital Controller,” in Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC), Mar. 2014, pp. 447-454.

- Koji Fujita, Daisuke Kanemoto, Kuniaki Yoshitomi, Keiji Yoshida, and Haruichi Kanaya, “UWB circularly polarized planar antenna on flexible substrate,” in Proc. IEEE MTT-S International Microwave Workshop Series on RF and Wireless Technologies for Biomedical and Healthcare Applications (IMWS-BIO), Dec. 2013, pp. 1-3.

- Wataru Yamamoto, Daisuke Kanemoto, Ramesh Pokharel, Keiji Yoshida, and Haruichi Kanaya, “A Low Power 2.4GHz LNA Operated in Subthreshold Region,” in Proc. International Conference on Information Engineering (ICIE 2013), Nov. 2013, pp. 74-78.

- Tomoya Ijiguchi, Daisuke Kanemoto, Kuniaki Yoshitomi, Keiji Yoshida, Akira Ishikawa, Shugo Fukagawa, Noriyuki Kodama, Akihiro Tahira, and Haruichi Kanaya, “Development of Circularly Polarized Planar Slot Antenna for 5.8 GHz-DSRC Application,” in Proc. Asia-Pacific Microwave Conference (APMC), Nov. 2013, pp. 1079-1081.

- Toru Okazaki, Daisuke Kanemoto, Ramesh Pokharel, Keiji Yoshida, and Haruichi Kanaya, “A Design Technique for a High-speed SAR ADC Using Non-binary Search Algorithm and Redundancy,” in Proc. Asia-Pacific Microwave Conference (APMC), Nov. 2013, pp. 506-508.

- Shoichiro Tsukamoto, Naoto Iizasa, Kuniaki Yoshitomi, Ramesh Pokharel, Keiji Yoshida, Reiji Hattori, Haruichi Kanaya, and Daisuke Kanemoto, “Development of a Rectenna for Batteryless Electronic Paper,” in Proc. IEEE TENCON, Oct. 2013, pp. 1-4.

- Yuharu Shinki, Daisuke Kanemoto, Keiji Yoshida, Ramesh Pokharel, Kuniaki Yoshitomi, and Haruichi Kanaya, “Wireless Power Transmission Circuit on a Small Planar Wide-Band Antenna,” in Proc. IEEE TENCON, Oct. 2013, pp. 1-4.

- Ken Miyahara, Daisuke Kanemoto, Ramesh Pokharel, Keiji Yoshida, and Haruichi Kanaya, “Development of Dual Band Digitally Controlled Oscillator using Fibonacci Sequence in 0.18 um CMOS Process,” in Proc. IEEE TENCON, Oct. 2013, pp. 1-4.

- Daisuke Kanemoto, Takahide Sato, and Makoto Ohki, “Analysis of Flash A/D Converter Gain Effect in Delta-Sigma Modulators,” in Proc. IEEJ International Analog VLSI Conference (AVIC'13), Oct. 2013, pp. 21-24.

- Takahide Sato, and Daisuke Kanemoto, “Buck Converter with Fast Output Voltage Transition using Current Regeneration Path,” in Proc. IEEJ International Analog VLSI Conference (AVIC'13), Oct. 2013, pp. 36-40.

- Haruichi Kanaya, Daisuke Kanemoto, Kazuhiro Hayakawa, Keiji Yoshida, Ramesh Pokharel, Kuniaki Yoshitomi, Akira Ishikawa, Shugo Fukagawa, Noriyuki Kodama, and Akihiro Tahira, “Multi-Band Miniaturized Slot Antenna with Two-Stage Bandpass Filter,” in Proc. IEEE Int. Symp. Antennas Propag. USNC-URSI Radio Sci. Meet. (APSURSI), Jul. 2013, pp.930-931.

- Daisuke Kanemoto, Keigo Oshiro, Haruichi Kanaya, and Keiji Yoshida, “An Implementation of Common Mode Free and New Switching Scheme SAR ADC,” in Proc. IEEE Symp. Low-Power High-Speed Chips (COOL CHIPS), Apr. 2013, Poster 21.

- Daisuke Kanemoto, Haruichi Kanaya, and Keiji Yoshida, “A Design Methodology of Low Power Delta-Sigma Modulator utilizing Opamp Sharing Technique,” in Proc. IEEE Symp. Low-Power High-Speed Chips (COOL CHIPS), Apr. 2013, Poster 20.

- Yoichi Ishizuka, Kenji Mii, Daisuke Kanemoto, and Tamotsu Ninomiya, “Frequency Response Analysis of Proposed Digital Control System for DPWM-POL,” in Proc. 15th Eur. Conf. Power Electron. Appl. (EPE’13-ECCE Europe), Sep. 2013, pp. 1-10.

- Yuki Yamashita, Daisuke Kanemoto, Haruichi Kanaya, Ramesh Pokharel, and Keiji Yoshida, “A CMOS Class-E Power Amplifier of 40% PAE at 5 GHz for Constant Envelope Modulation System,” in Proc. IEEE 13th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Jan. 2013, pp. 66-69.

- Takahiro Masumoto, Daisuke Kanemoto, Haruichi Kanaya, Ramesh Pokharel, and Keiji Yoshida, “Improving Linearization of a 5.2GHz Low Power Mixer in 0.18μm CMOS Process by Using Derivative Superposition Method,” in Proc. Asia-Pacific Microwave Conference (APMC), Dec. 2012, pp. 157-159.

- Keigo Oshiro, Daisuke Kanemoto, Haruichi Kanaya, Ramesh Pokharel, and Keiji Yoshida, “A Small Die Area and High Linearity 10-Bit Capacitive Three-Level DAC,” in Proc. IEEE Asia Pac. Conf. Circuits Syst. (APCCAS), Dec. 2012, pp. 164-167.

- Yuki Yamashita, Daisuke Kanemoto, Haruichi Kanaya, Ramesh Pokharel, and Keiji Yoshida, “A 5-GHz Fully Integrated CMOS Class-E Power Amplifier Using Self-Biasing Technique with Cascaded Class-D Driver,” in Proc. IEEE Int. Symp. Radio-Freq. Integr. Technol. (RFIT), Nov. 2012, pp. 245-247.

- Awinash Anand, Daisuke Kanemoto, Ghazal A. Fahmy, Ramesh Pokharel, Haruichi Kanaya, and Keiji Yoshida, “Feedforward Charge Injection Technique in a Continuous Time Delta-Sigma Modulator,” in Proc. IEEE TENCON, Nov. 2012, pp. 1-5.

- Haruichi Kanaya, Masataka Kato, Daisuke Kanemoto, Keiji Yoshida, Ramesh K. Pokharel, and Kuniaki Yoshitomi, “Development of 2.4GHz One-Sided Directional Slot Antenna with 2-Stage Bandpass Filter,” in Proc. IEEE Int. Symp. Antennas Propag. (APS/URSI), Jul. 2012, pp.1-2.

- Daisuke Kanemoto, Haruichi Kanaya, and Keiji Yoshida, “A Design Methodology for High-Performance D/A Converter utilizing Optimized Weights,” in Proc. IEEE Symp. Low-Power High-Speed Chips (COOL CHIPS), Apr. 2012, Poster 18.

- Ghazal Fahmy, Daisuke Kanemoto, Haruichi Kanaya, Ramesh Pokharel, and Keiji Yoshida, “A Third Order Delta-Sigma Modulator with Shared Opamp Technique for Wireless Applications,” in Proc. The 17th Workshop on Synthesis And System Integration of Mixed Information Technologies (SASIMI), Mar. 2012, pp. 466-467.

- Manabu Ishihara, Ramesh Pokharel, Abhishek Tomar, Daisuke Kanemoto, Haruichi Kanaya, and Keiji Yoshida, “Development of 13bit Digitally Controlled Oscillator using Fibonacci Sequence in 0.18um CMOS Process,” in Proc. Asia-Pacific Microwave Conference (APMC), Dec. 2011, pp. 1634-1637.

- Hirofumi Kuwamoto, Ruibing Dong, Daisuke Kanemoto, Ramesh K. Pokharel, Haruichi Kanaya, and Keiji Yoshida, “Ultra-wideband bandpass filter with notch and upper-band suppression,” in Proc. 2011 IET International Communication Conference on wireless Mobile & Computing, Nov. 2011, pp. 211-215.

- Daisuke Kanemoto, Toru Ido, and Kenji Taniguchi, “A 7.5mW 101dB SNR Low-Power High-Performance Audio Delta-Sigma Modulator Utilizing Opamp Sharing Technique,” in Proc. Int. SoC Des. Conf. (ISOCC), Nov. 2011, pp. 66-69.

- Kazuya Hokazono, Daisuke Kanemoto, Ramesh Pokharel, Abhishek Tomar, Haruichi Kanaya, and Keiji Yoshida, “A Low-Glitch and Small-Logic-Area Fibonacci Series DAC,” in Proc. IEEE 54th Midwest Symp. Circuits Syst. (MWSCAS), Aug. 2011, pp. 1-4.

- Haruichi Kanaya, Kazuhiro Hayakawa, Yuzou Nagata, Daisuke Kanemoto, Keiji Yoshida, Ramesh K. Pokharel, Kuniaki Yoshitomi, Akira Ishikawa, Shugo Fukagawa, and Akihiro Tahira, “Development of Dual Band Miniaturized Slot Antenna with 2-Stage Bandpass Filter,” in Proc. IEEE Int. Symp. Antennas Propag. (APSURSI), Jul. 2011, pp. 2761-2764.

- Takuya Hirabaru, Haruichi Kanaya, Daisuke Kanemoto, Pokharel Ramesh, Kuniaki Yoshitomi, and Keiji Yoshida, “Development of 900MHz band One-Sided Directional Antenna on Flexible Substrate,” in Proc. IEEE Int. Symp. Antennas Propag. (APSURSI), Jul. 2011, pp. 1008-1011.

- Satoshi Ijiguchi, Haruichi Kanaya, Daisuke Kanemoto, Keiji Yoshida, Ramesh Pokharel, Kuniaki Yoshitomi, Akira Ishikawa, Shugo Fukagawa, and Akihiko Tahira, “Development of One-Sided Directional Printed Slot Antenna for high-band UWB systems,” in Proc. IEEE Int. Symp. Antennas Propag. (APSURSI), Jul. 2011, pp. 1474-1477.

- Daisuke Kanemoto and Kenji Taniguchi, “Low Cost Implementation Technique of Delta-Sigma Analog-to-Digital Converters for Healthcare Applications,” in Proc. 7th International Conference on Ubiquitous Healthcare (u-Healthcare), Oct. 2010, pp. 3-4.

- Daisuke Kanemoto, Toru Ido, and Kenji Taniguchi, “A Power Reduction Technique for Continuous-Time ΔΣ Modulators,” in Proc. 1st Global COE Student Conference on Innovative Electronic Topics (SCIENT), Aug. 2008, O2-3.

- Makoto Osanai, Hirotsugu Okuno, Syunsuke Ohkura, Tukasa Ida, Daisuke Kanemoto, Jun Hasegawa, Naoki Kotani, Y. Hashimoto, and Tetsuro Ohkura, “Research and development for an advanced bio-imaging system,” in Proc. 1st Global COE International Symposium Electronic Devices Innovation (EDIS), Jan. 2008, pp.165-168.

- Daisuke Kanemoto, Toru Ido, and Kenji Taniguchi, “A Fully Digital RC Time Constant Auto-tuning Technique for Continuous-Time ΔΣ Modulators,” in Proc. 1st Global COE International Symposium Electronic Devices Innovation (EDIS), Jan. 2008, p.20.

- Habibul Kabir, Daisuke Kanemoto, and Kenji Taniguchi, “Modeling of CIFF Continuous-Time Sigma-Delta Modulator with the Influence of Finite Gain Bandwidth Induced Errors and Its Compensation,” in Proc. Int. Meet. Future Electron Devices Kansai (IMFEDK), Apr. 2007, pp. 117-118.

- Daisuke Kanemoto, Takeshi Ueno, and Kenji Taniguchi, “A Small Die Area Process Variation Auto-Tuning Structure for Continuous-Time Delta Sigma Modulators,” in Proc. Int. Meet. Future Electron Devices Kansai (IMFEDK), Apr. 2007, pp. 115-116.

D. 国内会議(査読有)Domestic Conferences (refereed)

- 兼本大輔, 牟田 修, 古川 浩,金谷晴一,大木 真, “IFサンプリング1bit A/D変換方式を採用した無線受信機の構成検討と試作による評価,” 第27回 回路とシステムワークショップ, 2014年8月, pp. 306-311.

E. 国際会議(査読無)International Conferences (not refereed)

- Daisuke Kanemoto, Shun Katsumata, Osamu Maida, and Tetsuya Hirose, “Study of Compressed Sensing EEG Measurement Framework with Eye-blink Artifact Removal Technique,” in proc. The 6th CiNet Conference, Feb. 2020.

- Yuki.Yamashita, Daisuke Kanemoto, Haruichi Kanaya, Ramesh Pokharel, and Keiji Yoshida, “A High-Efficient Class-E Power Amplifier for 5-GHz Constant Envelope Modulation System,” in proc. International Symposium on Information Science and Electrical Engineering, Jan. 2013, p.48.

F. 国内会議(査読無)Domestic Conferences (not refereed)

- 鷲見真太郎,兼本大輔, 廣瀬哲也, ”極低電圧デジタル回路に向けたフリップフロップ応用回路の検討,” 電子情報通信学会 集積回路研究会 学生・若手研究会 ,2025年12月.

- 大久保諒耶,三原柊平,瀬部 光,兼本大輔, 廣瀬哲也, ”微小温度差発電に向けたスイッチング電源回路に関する研究,” 電子情報通信学会 集積回路研究会 学生・若手研究会 ,2025年12月.

- 川上泰希朗,兼本大輔, 廣瀬哲也, ”適応バイアスオペアンプを用いた低消費電力増幅回路に関する研究,” 電子情報通信学会 集積回路研究会 学生・若手研究会 ,2025年12月.

- 松森拓馬,瀬部 光,兼本大輔, 廣瀬哲也, ”周波数誤差補正回路を搭載した膜型表面応力センサ向けCMOS 読み出し回路,” 電子情報通信学会 集積回路研究会 学生・若手研究会 ,2025年12月.

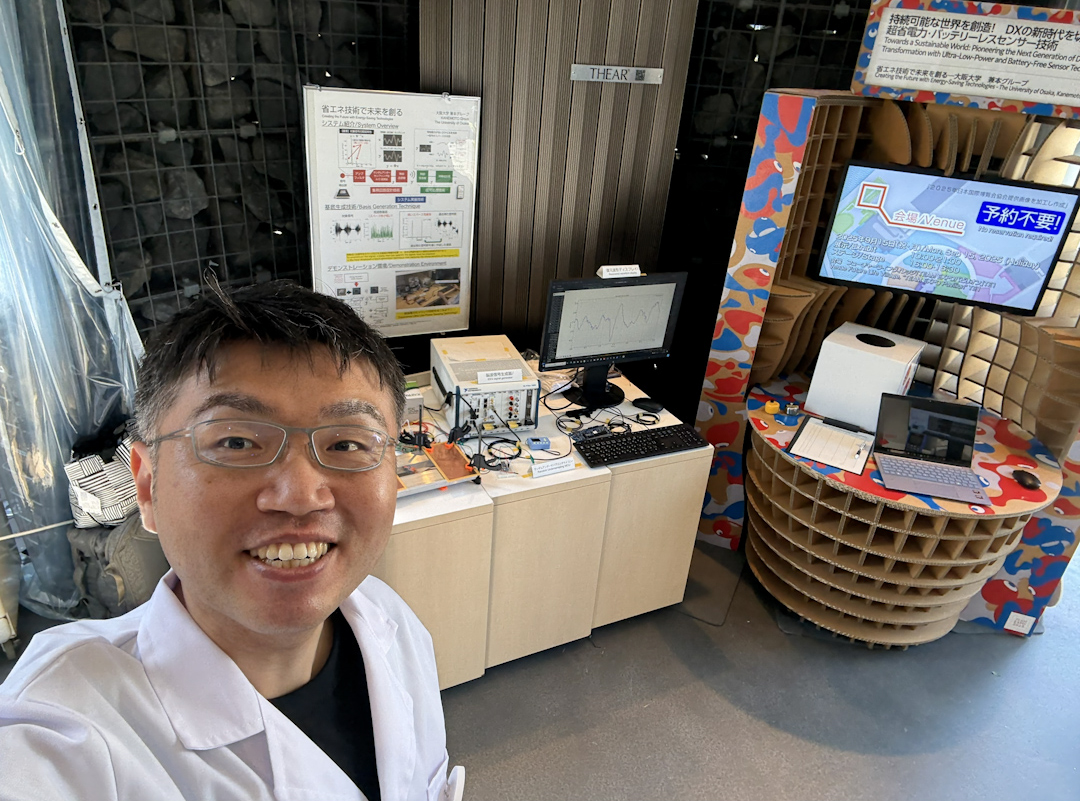

- 兼本大輔, 吉本風音,本持翔大, 廣瀬哲也, ”圧縮センシングによるハードウェア・信号処理融合型省電力無線脳波伝送システム 〜 万博会場における屋外検証:体温・外気温差から得られる僅少エネルギーのみで動作 〜,” 信学技報(デザインガイア2025) , vol. 125, no. 260, VLD2025-39,pp. 117-122, 2025年12月. デザインガイア優秀ポスター賞 受賞

- 立花春樹, 兼本大輔,松本拓真,廣瀬哲也,”split CDACを用いたランダムアンダーサンプリング型SARADCの基礎検討,” 第209回SLDM研究発表会(SLDM WIP Forum 2025),[2], 2025年11月.

SLDM 研究発表会 WIP 最優秀賞 受賞

吉本風音, 兼本大輔,廣瀬哲也,”僅かな温度差で動作する圧縮センシング型無線脳波センシングに向けた基礎検討,” 第209回SLDM研究発表会(SLDM WIP Forum 2025),[8], 2025年11月. IEEE CAS Society Kansai Chapter Best Student Presentation Award 受賞

兼本大輔,松本拓真,藤田雅幸,本持翔大,廣瀬哲也,”LSIとシステムを融合した圧縮センシング型バッテリーレス無線計測技術開発の取り組み

〜大阪・関西万博での展示予告〜,” LSIとシステムのワークショップ 2025 ,S41, 2025年5月.

兼本大輔, 瀧本英智, 廣瀬哲也, ”圧縮センシングにおける信号類似性の活用 〜 省電力無線脳波計測回路システム実現に向けた取り組み 〜,” 信学技報(デザインガイア2024) , vol. 124, no. 247, VLD2024-42,pp. 89-94, 2024年11月. 電子情報通信学会 VLD研究会優秀技術報告賞,情報処理学会 SLDM研究会 2024年度優秀発表賞,および情報処理学会 SLDM研究会 2024年度優秀論文賞 受賞

三井健司,兼本大輔, 廣瀬哲也, ”ランダムアンダーサンプリング型圧縮センシング脳波計測システムにおける低雑音アンプの消費電力低減手法,” 信学技報(デザインガイア2024) , vol. 124, no. 248, ICD2024-49,pp. 26-31, 2024年11月.

松本拓真,兼本大輔,奥村 渡,松原利空,廣瀬哲也, ”圧縮センシングを活用した無線脳波計測システムにおけるランダムアンダーサンプリング型SARADCの開発,” 信学技報(デザインガイア2024) , vol. 124, no.247, VLD2024-44,pp.100-104, 2024年11月.

吉川行人,兼本大輔,廣瀬哲也, ”無線脳波計のためのスケーラブルチョッパーオートゼロアンプに関する研究,” 信学技報(デザインガイア2024) , vol. 124, no. 247, VLD2024-48,pp. 120-125, 2024年11月.

山本智也,兼本大輔,津永亮多,廣瀬哲也, ”圧縮センシングと連鎖生成雑音マスキングを活用したセキュリティシステムにおける設計手法の検証,” 信学技報(デザインガイア2024) , vol. 124, no. 247, VLD2024-49,pp.126-130, 2024年11月.

本持翔大,兼本大輔,廣瀬哲也, ”圧縮センシングにおける無線脳波計測を想定したSimulated Annealingの適用,” 信学技報(デザインガイア2024) , vol. 124, no. 247, VLD2024-43,pp. 95-99, 2024年11月.

鷲見 真太郎,瀬部 光,兼本大輔,廣瀬哲也,”極低電圧NAND回路を用いたDフリップフロップ,” 電子情報通信学会 ソサイエティ大会,C-12-18,2024年9月.

栗栖 直己,瀬部 光,兼本大輔,廣瀬哲也,”熱電発電素子に向けた極低電圧ワンショットパルスジェネレータ,” 電子情報通信学会 ソサイエティ大会,C-12-17,2024年9月.

亀山 凜,瀬部 光兼本大輔,廣瀬哲也,”光エネルギーハーベスティングに向けた双方向SC型電源回路,” 電子情報通信学会 ソサイエティ大会,C-12-16,2024年9月.

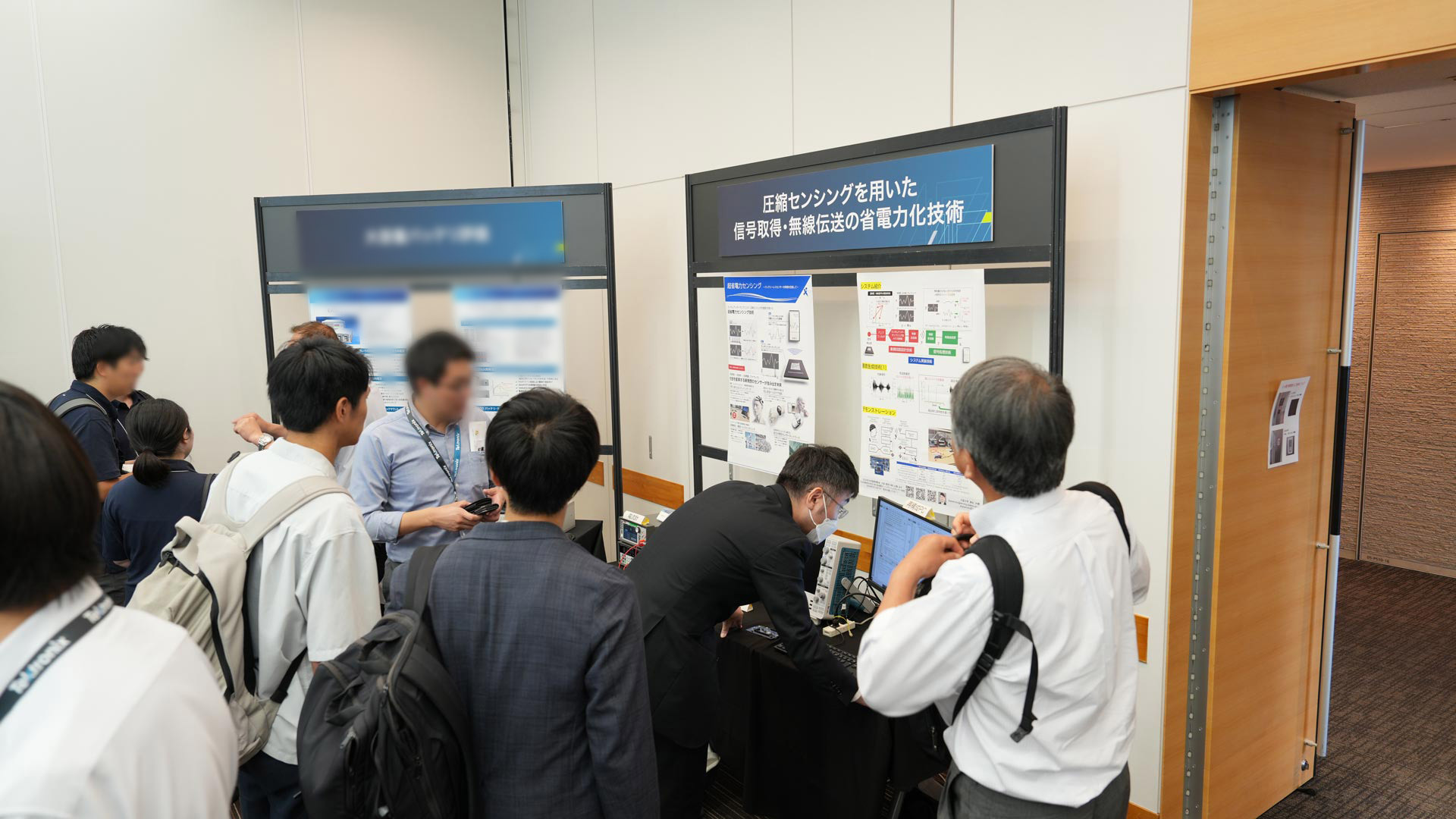

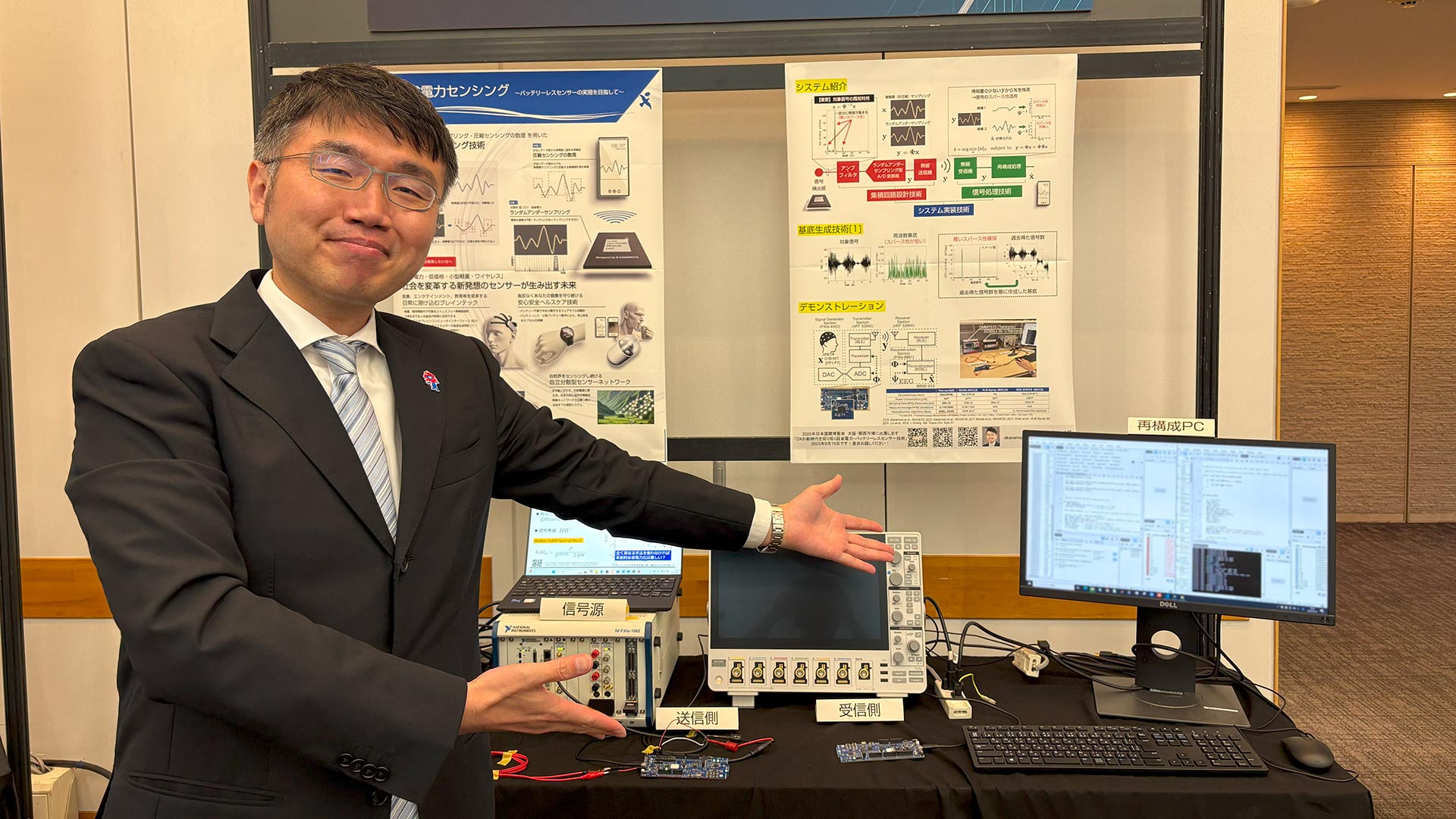

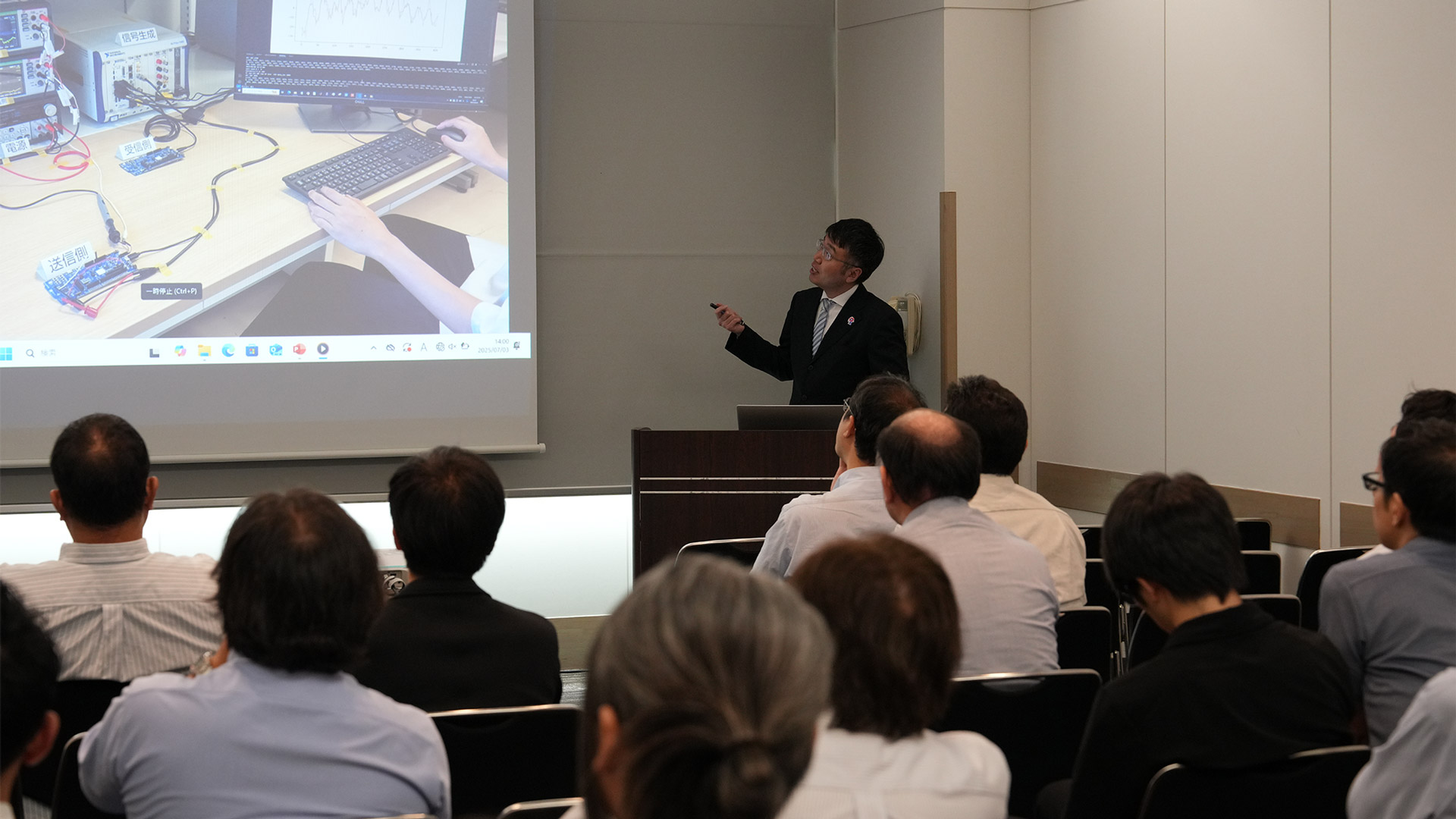

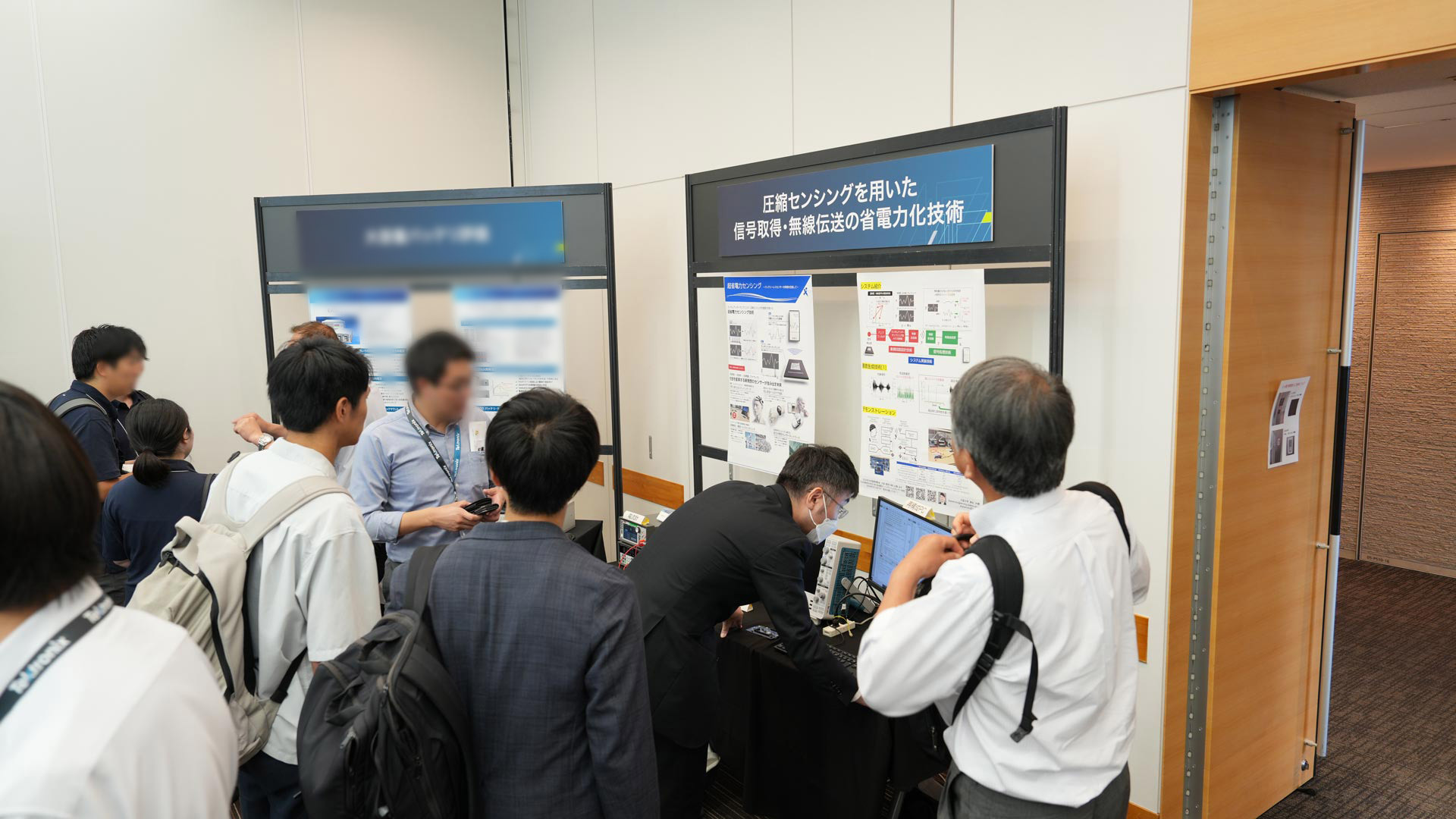

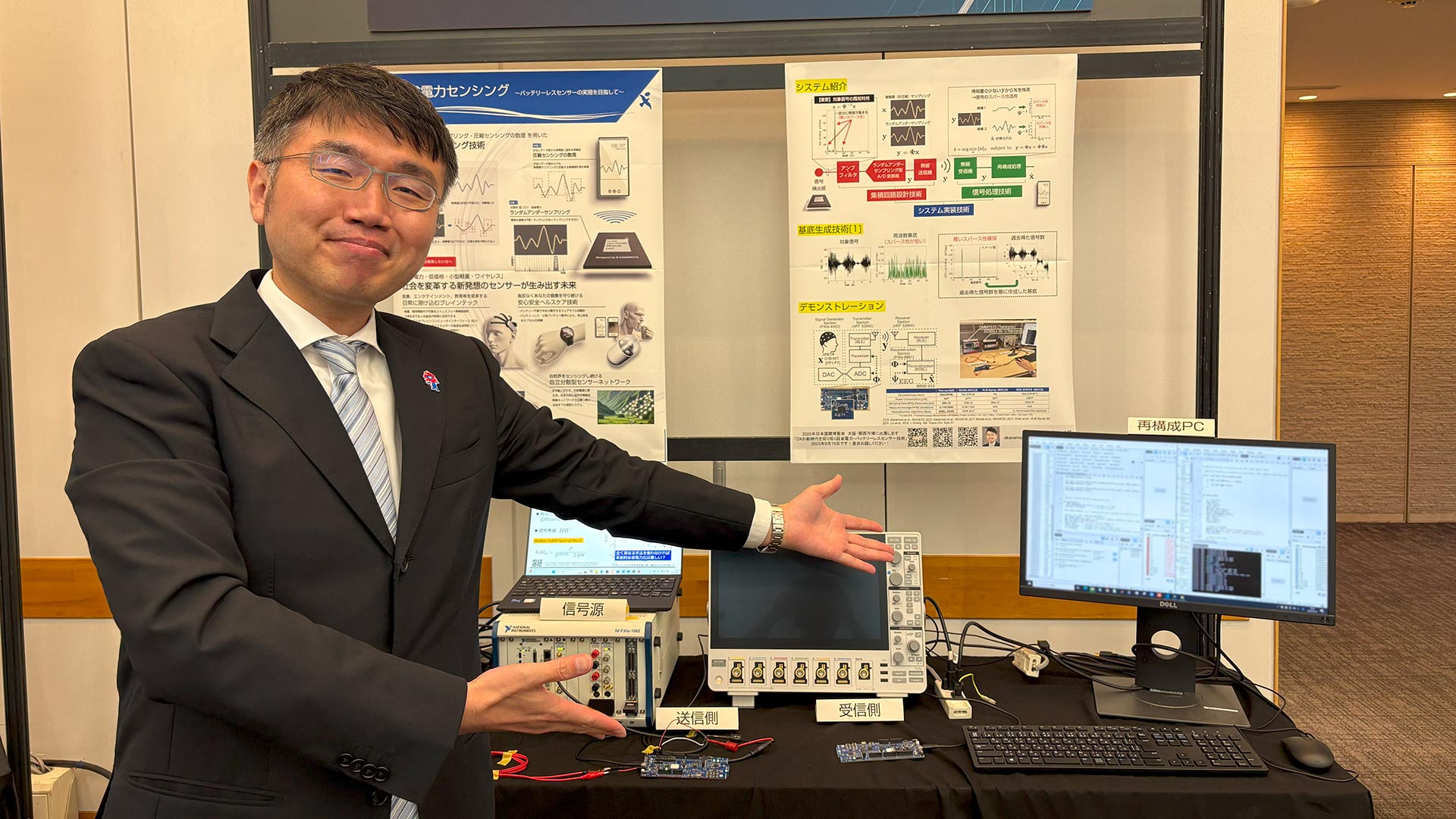

兼本大輔, “超省電力センシング〜バッテリーレスセンサーの実現を目指して〜,” イノベーションジャパン2024, 2024年8月22日23日.

兼本大輔,瀧本英智,三井健司,宮田拓弥,廣瀬哲也,”僅かな温度差で動作するバッテリーレス無線脳波計 〜ランダムアンダーサンプリングと圧縮センシングの数理を活用したLSIからシステムまで〜,” LSIとシステムのワークショップ 2024 ,S32, 2024年5月. 最優秀ポスター賞(一般部門)

鷲見真太郎,瀬部 光,奥村知央,兼本大輔,Chen Po-Hung,廣瀬哲也, ”リカーシブ・スタッキング・ボディ・バイアス技術を用いた極低電圧CMOS論理回路,” LSIとシステムのワークショップ 2024,S11 , 2024年5月. 優秀ポスター賞(学生部門)

瀬部 光,兼本大輔,廣瀬哲也,”60 mV以下の極低電圧で動作する微小温度差発電のためのフルオンチップ電源回路,” LSIとシステムのワークショップ 2024 ,S29, 2024年5月. 優秀ポスター賞(学生部門)

三井健司,兼本大輔,廣瀬哲也,”ウェアラブル脳波計実現に向けたランダムアンダーサンプリング型圧縮センシングウェアラブル脳波計測システムにおける低消費電力LNAの実測及びその解析,” LSIとシステムのワークショップ 2024 ,S26, 2024年5月.

山本智也, 兼本大輔, 桝田浩禎, 廣瀬哲也, ”心音計測システムへのランダムアンダーサンプリングを活用した圧縮センシング適用に関する考察,” 信学技報(デザインガイア2023) , vol. 123, no. 258, VLD2023-66,pp.187-191, 2023年11月.

宮田拓弥,兼本大輔,廣瀬哲也,”復元時に得られたパラメータを再利用するBSBL アルゴリズムを活用した圧縮センシングフレームワーク,” 電子情報通信学会 ソサイエティ大会,A-1-6,2023年9月.

松原利空,兼本大輔,廣瀬哲也,”連鎖圧縮センシングにおける脳波辞書適用による成功確率の改善,” 電子情報通信学会 ソサイエティ大会,A-1-7,2023年9月.

松本 香,池田隆希,瀬部 光,黒木修隆,沼 昌宏,兼本大輔,廣瀬哲也,”デジタルMPPT制御を用いた小型PVセル向けオンチップ昇圧コンバータ,” LSIとシステムのワークショップ2023, 2023年5月10日.

原田勇輝,兼本大輔,廣瀬哲也, “脳波を用いた感情認識システムにおける無線送信データ削減手法および実装に関する検討,” 電子情報通信学会 電子情報通信学会技術研究報告, vol. 122, no. 353, pp. 40-44, 2023年1月.

瀬部 光,兼本大輔,廣瀬哲也,”極低電圧熱エネルギーハーベスティングに向けた50mV以下の低電圧で動作する昇圧コンバータ,” 電子情報通信学会 集積回路研究専門委員会 集積回路研究会,pp.21-26,2022年8月.

谷上輝來,瀬部 光,兼本大輔,廣瀬哲也,”振動エネルギーハーベスティングに向けたバイアスフリップ整流回路の設計,” LSIとシステムのワークショップ2022,PS-16,2022年5月.

糸田川佳克,渥美光真,瀬部 光,兼本大輔,廣瀬哲也,”サブスレッショルド領域動作MOSFETを利用した極低消費電力温度センサ回路に関する研究,” LSIとシステムのワークショップ2022,PS-17,2022年5月.

水田拓海,池田隆希,瀬部 光,兼本大輔,廣瀬哲也,”低電圧CMOS発振回路のデジタル制御技術の検討,” LSIとシステムのワークショップ2022,PS-23,2022年5月.

西川晃弘,兼本大輔,三井健司,廣瀬哲也,”FVFを利用したリップル電圧の基本波・高調波成分除去が可能な低消費電力LDO,” 電子情報通信学会 総合大会,A-6-3,2022年3月.

津永亮多,兼本大輔,永井孝太郎,廣瀬哲也,”圧縮センシングを用いた脳波計測フレームの電子すかし暗号システムにおける DoS 攻撃耐性について,” 電子情報通信学会 総合大会,A-19-2,2022年3月.

岡部勇樹,兼本大輔,廣瀬哲也, “圧縮センシングを用いた低消費電力脳波計測フレームワークにおけるサンプリング系列比較,” 電子情報通信学会 総合大会,A-1-16,2022年3月.

永井孝太郎,兼本大輔,廣瀬哲也,大木 真,”BSBL アルゴリズムを用いた脳波圧縮センシングに適した辞書行列の解明,” 電子情報通信学会 総合大会,A-17-3, 2022年3月.

松村侑紀,兼本大輔,毎田 修,廣瀬哲也, “圧縮センシングを活用した心電図計測フレームワークの一設計法,” 電子情報通信学会 デザインガイア 電子情報通信学会技術研究報告, vol. 121, no. 277, pp. 99-104, 2021年12月.

三井健司,兼本大輔,毎田 修,廣瀬哲也,”FVFを応用したPSRR帯域拡張回路を搭載した脳波計測ウェアラブルデバイス向け低消費LDO,” 電子情報通信学会 デザインガイア 電子情報通信学会技術研究報告, vol. 121, no. 277, pp. 7-12, 2021年12月.

兼本大輔, “軽量ウェアラブルデバイス実現のためのセンシングフレームワーク,” イノベーションジャパン2021, 2021年8月-9月.

渥美光真,瀬部 光,中野太地,池田隆希,毎田 修,兼本大輔,廣瀬哲也, ”高精度参照電流源回路を不要とする品質劣化モニタセンサLSI”, LSIとシステムのワークショップ2021, PS-16, 2021年5月.

三原柊平,瀬部 光,毎田 修,兼本大輔,廣瀬哲也, ”微小温度差発電のための極低電圧昇圧コンバータ用ドライバ回路”, LSIとシステムのワークショップ2021, PS-15, 2021年5月.

笹谷昌平,中野太地,瀬部 光,毎田 修,兼本大輔,廣瀬哲也, ”超低消費電力で動作するオンチップ電圧検知回路の設計”, LSIとシステムのワークショップ2021, PS-14, 2021年5月.

岡部勇樹,兼本大輔,望月智弥,毎田 修,廣瀬哲也,”圧縮センシングを用いた低消費電力脳波計測フレームワークのサンプリング間隔の検討,” 電子情報通信学会 VLSI設計技術研究会 電子情報通信学会技術研究報告, vol. 120, no. 337, pp.80-84, 2021年1月.

奥村 渡,兼本大輔,毎田 修,廣瀬哲也,”OD-ICAを利用した圧縮センシング脳波計測フレームワークにおけるICAアルゴリズムの比較,” 電子情報通信学会 VLSI設計技術研究会 電子情報通信学会技術研究報告, vol. 120, no. 337, pp.75-79, 2021年1月.

松本 香,黒木修隆,沼 昌宏,毎田 修,兼本大輔,廣瀬哲也,”ヒステリシスコンパレータを使ったアクティブダイオードの評価,” 電子情報通信学会 ICD/CAS研究会 学生・若手研究会, P-15, 2020年12月.

瀬部 光,池田隆希,中野太地,毎田 修,兼本大輔,廣瀬哲也,”超低電圧で動作する基本論理ゲートとその応用,” 電子情報通信学会 ICD/CAS研究会 学生・若手研究会, P-14, 2020年12月.

池田隆希,瀬部 光,中野太地,毎田 修,兼本大輔,廣瀬哲也,”逐次比較型最大電力点追従制御を用いた小型太陽電池向け昇圧システム,” 電子情報通信学会 ICD/CAS研究会 学生・若手研究会, P-13, 2020年12月.

中野太地,池田隆希,瀬部 光,毎田 修,兼本大輔,廣瀬哲也,”RFエネルギーハーベスティングに向けた極低電圧AC-DCコンバータの検討,” 電子情報通信学会 ICD/CAS研究会 学生・若手研究会, P-12, 2020年12月.

西 雅也,肥田壮太郎,松本 香,黒木修隆,沼 昌宏,毎田 修,兼本大輔,廣瀬哲也,”極低電圧で動作するスイッチトキャパシタ型昇圧システムに向けたドライバ回路,” 電子情報通信学会 ICD/CAS研究会 学生・若手研究会, P-08, 2020年12月.

肥田壮太郎,L. Y. GYUN, 西 雅也,松本 香,黒木修隆,沼 昌宏,毎田 修,兼本大輔,廣瀬哲也, “高効率パワーマネジメントシステムに向けた超低消費電力レギュレータの検討,” 電子情報通信学会 ICD/CAS研究会 学生・若手研究会, P-07, 2020年12月.

毎田 修,兼本大輔,廣瀬哲也, “ホウ素添加ホモエピタキシャル成長ダイヤモンド薄膜の過渡光容量法を用いた結晶欠陥評価,” 2020年日本表面真空学会学術講演会, 1P62, 2020年11月.

毎田 修,兼本大輔,廣瀬哲也, “高濃度ホウ素ドープダイヤモンド多層膜クラスター構造の作製とその評価,” 2020年日本表面真空学会学術講演会, 1P63, 2020年11月.

原田勇輝,兼本大輔,大木 真,毎田 修,廣瀬哲也, “圧縮センシングを用いた低消費電力カプセル内視鏡システム実現のための設計指針に関する検討,” 電子情報通信学会 デザインガイア 電子情報通信学会技術研究報告, vol. 120, no. 235, pp. 95-100, 2020年11月.

佐藤太河,兼本大輔,勝俣 駿,毎田 修,廣瀬哲也, “圧縮センシングを用いた脳波計測フレームワークに搭載するアナログ回路で生じるノイズが信号復元に与える影響,” 電子情報通信学会 ソサイエティ大会,A-6-2,2020年9月.

勝俣 駿,兼本大輔,大木 真, “圧縮センシングを用いた脳波復元フレームワークにおけるICA処理位置の違いによる瞬目アーチファクト除去への効果,” 電子情報通信学会 総合大会,A-8-7, 2020年3月.

Chen Brendon,兼本大輔,毎田 修,廣瀬哲也, “Study of Digital Circuit Design of Independent Component Analysis for Compressed Sensing Electroencephalogram Signal Processing,” 電気学会 電子回路研究会,ECT-020-002, 2020年1月.

勝俣 駿,兼本大輔,大木 真, “独立成分分析と外れ値検知を用いた圧縮センシングによる脳波の復元”電気学会 電子回路研究会,ECT-020-001 , 2020年1月.

沖田 翔,増田創太,松本 香,黒木修隆,沼 昌宏,毎田 修,兼本大輔,廣瀬哲也, “ワイヤレス給電システムの位置自由度を改善するパワーマネジメント回路に関する研究,” 電子情報通信学会 ICD/CAS研究会 学生・若手研究会, 2019年12月.

矢倉佳樹, 佐藤孝憲, 松本 香, 黒木修隆, 沼 昌宏, 毎田 修, 兼本大輔, 廣瀬哲也, “低電圧エネルギーハーベスティングシステムに向けた超低消費電力電圧モニタ回路,” 電子情報通信学会 ICD/CAS研究会 学生・若手研究会, 2019年12月.

木村亮平, 浅野大樹, 松本 香, 黒木修隆, 沼 昌宏, 毎田 修, 兼本大輔, 廣瀬哲也, “リアルタイムクロックに向けた超低消費電力32 kHz水晶発振回路,” 電子情報通信学会 ICD/CAS研究会 学生・若手研究会, 2019年12月.

兼本大輔, “圧縮センシングを活用した無線脳波計測デバイス,” ACT japanフォーラム, 2019年12月.

毎田 修,兼本大輔,廣瀬哲也,“過渡光容量分光法を用いたボロンドープダイヤモンド薄膜の非輻射欠陥評価,” 2019年日本表面真空学会学術講演会, 2P07, 2019年10月.

毎田 修,兼本大輔,廣瀬哲也, “(111)ダイヤモンド基板上ホモエピタキシャル成長におけるメタン濃度および基板オフ方向依存性,” 2019年日本表面真空学会学術講演会,2P06,2019年10月.

高木茂孝,ニコデムスレディアン,兼本大輔, “「システムLSIに関連する雑音の影響を低減するための技術調査専門委員会」活動報告,”電気学会 電子回路研究会, ECT-019-037, 2019年6月.

勝俣 駿,兼本大輔,永井孝太郎,大木 真, “圧縮センシングと独立成分分析を用いた低消費電力脳波計測システム,” LSIとシステムのワークショップ2019, No.30, 2019年5月.

望月智弥, 兼本大輔, 勝俣 駿, 大木 真, “独立成分分析を活用した圧縮センシングフレームワークのためのA/D変換に必要な分解能の検討,” LSIとシステムのワークショップ2019, No.29, 2019年5月.

遠藤央瑠人, 兼本大輔, 景山知哉, 牟田 修, 大木 真, “低消費電力無線受信機のためのヒステリシスコンパレータとディザーを活用したADCの検討,” 電気学会 電子回路研究会, ECT-018-100, 2018年12月.

望月智弥, 兼本大輔, 遠藤央瑠人, 勝俣 駿, 大木 真, “圧縮センシングと独立成分分析を活用した脳波計測デバイスに用いるA/D変換器の検討,” 電気学会 電子回路研究会, ECT-018-099, 2018年12月.

勝俣 駿, 兼本大輔, 大木 真, “復元前に独立成分分析を活用する新しい脳波の圧縮センシングフレームワーク,” 電気学会 電子回路研究会, ECT-018-098, 2018年12月.

萱沼浩称, 兼本大輔, 大木 真, “適応非整数次微積分フィルタを用いた画像の混合雑音除去,” 電子情報通信学会 ソサイエティ大会, A-16-2, 2018年9月.

雨宮享平, 兼本大輔, 大木 真, “混合ノルムを用いたスパースNMPCFによる歌声分離,” 電子情報通信学会 ソサイエティ大会, A-5-7, 2018年9月.

米山聖人, 兼本大輔, 大木 真, “適応フィルタを用いた画像の雑音除去時に生じるオーバーシュートの低減,” 第37回日本生体医工学会 甲信越支部大会, pp. 33-34, 2017年11月.

牧 俊輝, 兼本大輔, 大木 真, “p 乗ノルムを考慮したスパースモデリングに基づく画像の雑音除去,” 第37回日本生体医工学会 甲信越支部大会, pp. 35-36, 2017年11月.

佐藤達朗,大木 真,兼本大輔, “圧縮センシングの音声認識への応用,” 電子情報通信学会 総合大会,情報・システムソサイエティ特別企画, ISS-P-123, 2017年3月.

高木茂孝,ニコデムスレディアン,兼本大輔, “「システムLSIにおけるディジタル雑音の伝搬メカニズム調査専門委員会」活動報告,” 電気学会 電子回路研究会, ECT-016-052, 2016年6月.

中澤康二, 兼本大輔, 河野晋治, 今村 光, 服部一裕, 大木 真, “マイクロ波共振器を利用した食品凍結モニタリング装置の検討,” 電子情報通信学会 総合大会, A-1-5, 2016年3月.

深澤直樹,兼本大輔, 大木 真, “圧縮センシングを用いたサブナイキスト・サンプリングシステムにおける圧縮率と復元率に関する考察,” 電子情報通信学会 総合大会, A-1-4, 2016年3月.

深澤直樹,兼本大輔, 大木 真, “サブナイキスト・サンプリングシステムにおける入力情報量と復元率に関する考察,” 日本生体医工学会 甲信越支部大会, 2015年10月.

牧 俊輝,二木秀治,兼本大輔, 大木 真, “3D NLMP適応フィルタによる動画像の雑音除去の評価,” 日本生体医工学会 甲信越支部大会, 2015年10月.

遠藤真輝, 佐藤隆英, 兼本大輔, “多チャネル生体信号増幅回路における基準入力端子の共有による小面積・低電力化,” 電気学会 電子回路研究会, ECT-15-041, 2015年3月.

Shingo Nakamura, Haruichi Kanaya, Daisuke Kanemoto, “High-Efficiency Power Amplifier with PAE-Optimized Impedance matching circuit,” バイオメカニクス研究センター&エレクトロニクス実装学会 九州支部 合同研究会, 2015年2月.

福重翔太,牟田 修,兼本大輔,古川 浩, “ディジタル通信受信機へのヒステリシスA/D変換器の適用と特性評価,” 電子情報通信学会 通信方式研究会 電子情報通信学会技術研究報告, vol. 114, no. 463, pp. 37-42, 2015年2月.

兼本大輔,佐藤隆英,大木 真, “内部A/D変換器の等価ゲインを活用したデルタシグマ変調器,” 電気学会 電子回路研究会, ECT-14-102, 2014年12月.

兼本大輔,大木 真, “軽量脳波測定ヘッドギアに用いる低消費電力デルタシグマA/D変換LSI,” 日本生体医工学会 甲信越支部大会, 2014年10月.

中澤康二,兼本大輔,佐藤隆英,大木真, “太陽電池で動作するBluetoothのためのパワーアンプの設計,” 日本生体医工学会 甲信越支部大会, 2014年10月.

佐藤達朗,舘岡高志,兼本大輔,大木 真, “NLMP適応アルゴリズムによる雑音除去の評価,” 日本生体医工学会 甲信越支部大会, 2014年10月.

福重翔太,牟田 修,兼本大輔,古川 浩, “シングルキャリア伝送におけるコンパレータヒステリシスを考慮したA/D変換器の非線形歪み低減手法と特性評価,” 電子情報通信学会 無線通信システム研究会 電子情報通信学会技術研究報告, vol. 114, no. 254, pp. 105-110, 2014年10月.

福重翔太,牟田 修,兼本大輔,古川 浩, “無線通信受信機用A/D変換器における非線形歪みの軽減手法に関する検討,” 電子情報通信学会 ソサイエティ大会, B-5-44, 2014年9月.

小高 晃,佐藤隆英,兼本大輔, “集積化電源回路の小面積化設計の検討,” 電気学会 C部門大会, 2014年9月.

兼本大輔,佐藤隆英,大木 真, “外乱により発生する雑音がデルタシグマ変調器へ与える影響,” 電気学会 C部門大会, 2014年9月.

兼本大輔,佐藤隆英,大木 真, “内部A/D変換器の等価ゲインを活用したデルタシグマ変調器設計,”電子情報通信学会 アナログRF研究会,2014年7月.

中村真悟,兼本大輔,ポカラメシュ,吉田啓二,金谷晴一, “アンテナとの一体化設計による5GHz帯高効率電力増幅器の開発,” 電子情報通信学会 総合大会, C-12-27, 2014年3月.

長田岳志,佐藤隆英,兼本大輔, “レベルシフト回路を用いたリングオシレータの発振周波数の高周波化,” 電気学会 電子回路研究会, ECT-14-050, 2014年3月.

有賀祐太,佐藤隆英,兼本大輔, “ブートストラップ回路の削減によるチャージポンプ回路の高効率化,” 電気学会 電子回路研究会, ECT-14-036, 2014年3月.

兼本大輔,牟田 修,古川 浩,佐藤隆英,大木 真, “1bit分解能A/D変換器を用いた無線機の検討,” 電気学会 電子回路研究会, ECT-14-041, 2014年3月. 電気学会 電子・情報・システム部門 技術委員会奨励賞

小椋 翔, 兼本大輔,大木 真, “方向推定型補間の改良,” 電子情報通信学会 総合大会, D-11-55, 2014年3月.

一橋和真, 兼本大輔,大木 真, “可変フィルタマスクを用いたLMP適応アルゴリズム,” 電子情報通信学会 総合大会, D-11-46, 2014年3月.

Wataru Yamamoto, M.A.Abdelghany, Daisuke Kanemoto, Rames K.Pokharel, Keiji Yoshida, and Haruichi Kanaya, “Gain Improvement Using Positive Feedback for Subthreshold LNA,” バイオメカニクス研究会&エレクトロニクス実装学会 九州支部合同研究会, O.26, 2014年2月.

藤田浩司, 兼本大輔,吉田啓二,吉富邦明,金谷晴一, “UWB円偏波フレキシブルアンテナ,” バイオメカニクス研究会&エレクトロニクス実装学会 九州支部合同研究会, O.14, 2014年2月.

一見貴文,佐藤隆英, 兼本大輔, “2ステップ充電技術を用いたチャージポンプ回路のデューティー比制御による出力電圧可変,” 電気学会 電子回路研究会, ECT-14-002, 2014年1月.

三井健司,野中廣茂, 兼本大輔, 石塚洋一, “数十nsecオーダーの応答時間を目標としたPOL用ディジタル制御回路における周波数特性解析,” 電子情報通信学会 電子通信エネルギー技術研究会 電子情報通信学会技術研究報告, vol. 113, no. 392, pp.49-54, 2014年1月.

兼本大輔, 三井健司,野中廣茂,石塚洋一,大木 真, “内部A/D変換器の分解能・レイテンシがDC-DCコンバータに与える影響,” 電子情報通信学会 電子通信エネルギー技術研究会 電子情報通信学会技術研究報告, vol. 113, no. 392, pp.55-60, 2014年1月.

福重翔太, 牟田 修, 兼本大輔, 古川 浩, “オフセットQPSK受信機におけるADC非線形歪みの軽減手法,” 電気学会 電気関係学会 九州支部第66回連合大会, 2013年9月.

中村真悟,兼本大輔, 吉田啓二,ポカレルラメシュ,金谷晴一, “アンテナとの一体型設計による5.2GHz用電力増幅器の高効率化,” 電気学会 電気関係学会九州支部第66回連合大会, 2013年9月.

兼本大輔, 佐藤隆英, 大木 真, “マルチビット量子化器が有するゲインを活用したデルタシグマ変調器の提案,” 電子情報通信学会 ソサエティ大会, A-1-8, 2013年9月. 電子情報通信学会 学術奨励賞

佐藤隆英, 宮崎想太郎, 一見貴文, 兼本大輔, “2ステップ充電技術を用いたチャージポンプの効率改善,” 電気学会 電子・情報・システム部門大会, pp. 1728-1732, 2013年9月.

兼本大輔, 佐藤隆英, 大木 真, “オペアンプシェアリング技術を用いたデルタシグマ変調器の一設計法,” 電気学会 電子回路研究会, ECT-13-057, 2013年7月. 平成25年 電気学会 電子・情報・システム部門研究会 優秀論文発表賞

兼本大輔, 牟田 修, 福永龍太, 古川 浩, 金谷晴一, 吉田啓二, “定包絡線変調受信機のための1bit量子化A/D変換器の構成と性能評価,” 電子情報通信学会 無線通信システム研究会 電子情報通信学会技術研究報告, vol.113, no.8, pp.119-124, 2013年4月.

金谷晴一,兼本大輔,ポカレルラメシュ,吉田啓二, “インピーダンス整合一体型高周波CMOS デバイスの開発,” バイオメカニクス研究センター&エレクトロニクス実装学会 九州支部合同研究会, S4, 2013年3月.

金谷晴一,石田竜也,兼本大輔,ポカレルラメシュ,吉田啓二, “高周波用オンチップパッシブデバイスの開発,” 電気学会 全国大会, 2013年3月.

井地口朋也,兼本大輔,金谷晴一,吉田啓二,Ramesh K. Pokharel,吉冨邦明,石川晶,深川秀午,児玉法行,多比良明弘, “5.8GHz-DSRC用平面型円偏波スロットアンテナの開発,” 電子情報通信学会 総合大会, B-1-54, 2013年3月.

藤田浩司,兼本大輔,金谷晴一,吉田啓二,Pokharel Ramesh, 吉富邦明, “UWB円偏波フレキシブルアンテナの開発,” 電子情報通信学会 総合大会, B-1-110, 2013年3月.

宮川晃尚,内田祐介,山下勇輝,兼本大輔,金谷晴一, “5GHz帯パワーアンプのモジュール化,” 第27回エレクトロニクス実装学会講演大会 エレクトロニクス実装学術講演大会講演論文集, vol. 27, pp.342-343, 2013年3月.

福元俊吏,Emad Tamman,兼本大輔,金谷晴一,吉田啓二,吉富邦明, “UWB用デュアルバンドモノポールアンテナの開発,” 第27回エレクトロニクス実装学会講演大会 エレクトロニクス実装学術講演大会講演論文集, vol. 27, pp. 468-470, 2013年3月.

石田竜也, 金谷晴一, ポカレルラメシュ, 兼本大輔, 吉田啓二, “CMOSプロセスを用いた60GHz帯小型バンドパスフィルタの開発,” 第27回エレクトロニクス実装学会講演大会 エレクトロニクス実装学術講演大会講演論文集, vol. 27, pp. 471-474, 2013年3月.

内田祐介, 宮川晃尚, 山下勇輝, 兼本大輔, 金谷晴一, “5GHz帯パワーアンプのデバイスシミュレーションおよび実証実験,”バイオメカニクス研究センター&エレクトロニクス実装学会 九州支部合同研究会, O9, 2013年3月.

兼本大輔, 大城啓吾, 金谷晴一, 吉田啓二, “SAR A/D変換LSIの低コスト実装法,” バイオメカニクス研究センター&エレクトロニクス実装学会 九州支部合同研究会, O10, 2013年3月.

牟田 修, 兼本大輔, 福永龍太, 古川 浩, “1bitADCを用いる無線シングルキャリア位相変調システムの伝送特性評価,” 電子情報通信学会 通信方式研究会 電子情報通信学会技術研究報告, vol. 112, no.485, pp.229-233, 2013年3月.

兼本大輔, 牟田 修, 古川 浩, 金谷晴一, 吉田啓二, “無線シングルキャリア位相変調信号に適した1bit A/D変換器の構成と性能評価,” 電子情報通信学会 通信方式研究会 電子情報通信学会技術研究報告, vol.112, no. 486, pp. 223-227, 2013年3月.

岡崎 透, 兼本大輔, 金谷晴一,ポカレルラメシュ, 吉田啓二, “高速SAR ADC実現のための設計手法の提案,” 電気学会 電子回路研究会, ECT-12-087, 2012年12月.

橋村亮介, ドンルイビン, ポカレルラメシュ, 兼本大輔, 金谷晴一, 吉田啓, “ハイパス特性を持ったUWB-IRトランスミッタ用CMOSオンチップバランの開発,” 電子情報通信学会 マイクロ波研究会 電子情報通信学会技術研究報告, vol. 112, no. 251, pp. 59-64, 2012年10月.

兼本大輔, 大城啓吾, 金谷晴一,吉田啓二, “外部中間参照電圧が不要な新型SAR ADCの提案,” 電気学会 電子回路研究会, ECT-12-081, 2012年10月.

福永龍太, 山下勇輝, 牟田 修, 兼本大輔, 金谷晴一, 吉田啓二, 古川 浩, “MIMOシングルキャリアシステムにおけるE級電力増幅信号のモデル化とシミュレーション評価,” 電子情報通信学会 九州支部大会, 08-1P-01, 2012年9月.

宮原 健, 兼本大輔, ポカレルラメシュ, 金谷晴一, 吉田啓二, “擬フィボナッチ数列を用いた広帯域LC-DCOの開発,” 電子情報通信学会 九州支部大会, 12-1P-03, 2012年9月.

山本 航, 兼本大輔, ポカレルラメシュ, 金谷晴一, 吉田啓二, “サブスレショルド領域を用いた2.4GHz低消費電力LNAの設計,” 電子情報通信学会 九州支部大会, 12-1P-05, 2012年9月.

岡崎 透, 兼本大輔, 金谷晴一, ポカレルラメシュ, 吉田啓二, “冗長性を持つ低消費電力・高信頼性SAR ADC,” 電子情報通信学会 九州支部大会, 12-1P-07, 2012年9月.

三井健司, 浜口亮太, 兼本大輔, 石塚洋一, “高速応答可能なDPWM制御POLのインターフェイス回路に関する研究,” 電子情報通信学会 九州支部大会, 12-2A-04, 2012年9月.

新木優花, 兼本大輔, ポカレルラメシュ, 吉冨邦明, 金谷晴一, 吉田啓二, “複数のノッチを有する小型モノポールワイドバンドアンテナの開発,” 電子情報通信学会 九州支部大会, 08-2P-05, 2012年9月.

井地口朋也, 兼本大輔, ポカレルラメシュ, 吉富邦明, 金谷晴一, 吉田啓二, 石川 晶, 深川秀午, 児玉法行, 多比良明弘, “5.8GHz-DSRC用平面型円偏波アンテナの開発,” 電子情報通信学会 九州支部大会, 08-2P-09, 2012年9月.

藤田浩司, 兼本大輔, ポカレルラメシュ, 吉富邦明, 金谷晴一, 吉田啓二, 石川 晶, 深川秀午, 児玉法行, 多比良明弘, “UWBフレキシブルアンテナの開発,” 電子情報通信学会 九州支部大会, 08-2P-11, 2012年9月.

塚本祥一朗, 兼本大輔, ポカレルラメシュ, 吉富邦明, 渡邊明彦, 高橋達也, 服部励治, 金谷晴一, 吉田啓二, “エナジーハーベスティング用レクテナの開発,” 電子情報通信学会 九州支部大会, 08-2P-12, 2012年9月.

山下勇輝, 兼本大輔, 金谷晴一, ラメシュポカレル, 吉田啓二, “注入同期を用いた5GHz帯カスコードE級CMOS PA,” 電子情報通信学会 総合大会, C-12-58, 2012年3月.

橋村亮介, ヌグロホプラプト, 兼本大輔, ラメシュポカレル, 金谷晴一, 吉田啓二, “低位相雑音, 広周波数可変範囲を持つ4 位相出力リング型DCOの開発,” 電子情報通信学会 総合大会, C-12-57, 2012年3月.

増本崇大, 兼本大輔, 金谷晴一, ラメシュポカレル, 吉田啓二, “差動型LNAの設計手法,” 電子情報通信学会 集積回路研究会 電子情報通信学会技術研究報告, vol. 111, no. 352, pp. 115-117, 2011年12月.

Haruichi Kanaya, Daisuke Kanemoto, Tamesh Pokharel, Keiji Yoshida, “Design of Transmission Line Based On-Chip Passive Elements,” Microwave Workshops & Exhibition MWE 2011, workshop 16, 2011年12月.

山下勇輝, 兼本大輔, ポカレルラメシュ, 金谷晴一, 吉田啓二, “5GHz帯高効率CMOS E級電力増幅器の開発,” 電気学会 電子回路研究会, ECT-11-087, 2011年10月.

外薗和也, 兼本大輔, ポカレルラメシュ, 金谷晴一, 吉田啓二, “トリボナッチ数列を用いたDACの開発,” 電気学会 電子回路研究会, ECT-11-076, 2011年10月.

大城啓吾, 兼本大輔, 金谷晴一, ポカレルラメシュ, 吉田啓二, “3値参照電圧を用いた容量DACの設計,” 電気学会 電子回路研究会, ECT-11-075, 2011年10月.

福元俊吏, 金谷晴一, 吉田啓二, 吉富邦明, 兼本大輔, ラメシュ ポカレル, “2つの阻止帯域を持つUWB用小型モノポールアンテナ,” 電子情報通信学会 九州支部大会, 10-2A-04, 2011年9月.

大城啓吾, 兼本大輔, ラメシュ ポカレル, 金谷晴一, 吉田啓二, “3進数を用いた8bitセグメント型容量DACの開発,” 電子情報通信学会 九州支部大会, 09-1P-06, 2011年9月.

増本崇大, ラメシュポカレル, 兼本大輔, 吉田啓二, 金谷晴一, “0.18μm CMOSプロセスを用いた低消費電力ミキサの線形性改善,” 電子情報通信学会 九州支部大会, 09-1P-05, 2011年9月.

橋村亮介, 兼本大輔, ラメシュ ポカレル, 金谷晴一, 吉田啓二, “低位相雑音,広周波数可変範囲を持つ4位相出力リング型DCOの開発,” 電子情報通信学会 九州支部大会, 09-1P-04, 2011年9月.

山下勇輝, 兼本大輔, ラメシュポカレル, 金谷晴一, 吉田啓二, “MEMSプロセスを用いた低損失インピーダンス整合回路の開発,” 電子情報通信学会 九州支部大会, 09-1P-02, 2011年9月.

石田竜也, 金谷晴一, 吉田啓二, ラメシュポカレル, 兼本大輔, “MEMSを用いた60GHz帯Band Pass Filterの開発,” 電子情報通信学会 九州支部大会, 09-1P-01, 2011年9月.

兼本大輔, ポカレルラメシュ, 金谷晴一, 吉田啓二, “一つのオペアンプで構成する二次のデルタシグマ変調器の提案,” 電子情報通信学会 総合大会, C-12-59, 2011年3月.

外薗和也, 久保川竜太, 兼本大輔, ポカレルラメシュ, 金谷晴一, 吉田啓二, “フィボナッチ数列を用いた低グリッチ・高精度DACの開発,” 電子情報通信学会 総合大会, C-12-39, 2011年3月.

池村充史, 兼本大輔, 井戸 徹, 谷口研二, “チャネル構成の変更可能なオーディオ用D級アンプの設計法,” 電気学会 電子回路研究会, ECT-11-008, 2011年1月.

田村 悠, 兼本大輔, 谷口研二, “デルタシグマ型D/A変換器に用いる循環型部分的DWA手法の提案,” 電気学会 電子回路研究会, ECT-11-002, 2011年1月.

磯部直己, 兼本大輔, 井戸 徹, 谷口研二, “時間量子化方式ADコンバータにおけるディザの最適化,” 電気学会 電子回路研究会, ECT-10-071, 2010年6月.

兼本大輔, 井戸 徹, 谷口研二, “連続時間型デルタシグマ変調器のための電流コントローラーを用いた時定数補正手法,” VDECデザイナーフォーラム2009, 2009年6月.

兼本大輔, 堀場洋輔, 井戸 徹, 谷口研二, “1つのopampで構成できる2次の連続時間型デルタシグマ変調器,” VDECデザイナーフォーラム2009, 2009年6月.

兼本大輔, “新しいトランジスタの利用法〜 How to makeからWhat to Makeへ、VDECからの産業創出を目指して 〜(パネルディスカッション),” VDECデザイナーフォーラム2009, 2009年6月.

堀場洋輔, 兼本大輔, 井戸 徹, 谷口研二, “1.5bit量子化器を用いたActive-Passive積分器による2次CT-DSMの構成法,” 電気学会 電子回路研究会, ECT-09-15, 2009年1月.

兼本大輔, “世界で活躍できるLSI研究者を目指して(パネルディスカッション),” VDECデザイナーフォーラム2007, 2007年9月.

兼本大輔,谷口研二, “連続時間型ΔΣモジュレータのための低電源電圧動作可能なアンプの提案,” 電気学会 電子回路研究会, ECT-07-42, 2007年6月.

兼本大輔,谷口研二, “連続時間型ΔΣモジュレータのための小面積時定数チューニング機構に関する研究,” 電気学会 電子回路研究会, ECT-07-41, 2007年6月.

Davico Giulio, Daisuke Kanemoto, Neviani Andrea, and Kenji Taniguchi, “Design methodology of SC low-pass filter,” 電子情報通信学会 シリコンアナログRF研究会, 2007年6月.

兼本大輔, 谷口研二, “新しい時定数チューニング法を用いたGSM用連続時間型ΔΣモジュレータの設計,” 電子情報通信学会 シリコンアナログRF研究会, 2007年6月.

兼本大輔, 谷口研二, “アクティブRC積分器の解析とフィードフォワード充電法の提案,” 電気学会 電子回路研究会, ECT-06-40, 2006年3月.

兼本大輔, 大倉俊介, 谷口研二, “同相除去比を強化した増幅器,” 電子情報通信学会 総合大会, A-1-12, 2005年3月.

兼本大輔, 大倉俊介, 谷口研二, “同相除去比を強化した増幅器,” 電気学会 電子回路研究会, ECT-05-25, 2005年3月.

G. 特許 Patents

- 兼本大輔, 津永亮多,“センシングデバイス、データ処理ユニット及びセンシングシステム,” 特願2023-217844, 出願日:令和5年12月25日.

- 兼本大輔, “信号圧縮装置、信号復元装置及び信号処理システム,” 特願2023-1730, 出願日:令和5年1月10日.

- 兼本大輔, 永井孝太郎, “信号圧縮装置、信号復元装置及び信号処理システム,” 特願2022-28896, 出願日:令和4年2月28日.

- 三井健司,兼本大輔, “定電圧回路及び電子機器,” 特願2021-193038, 出願日:令和3年11月29日.

- 兼本大輔,勝俣駿, “信号計測システム、計測信号処理装置及びプログラム,” 特願2020-13805, 出願日:令和2年1月30日.

- 兼本大輔, “フラッシュ型AD変換器、無線受信機及び無線通信システム,” 特願2019-100242, 出願日:令和元年5月29日.

- 兼本大輔, 牟田修, “1ビットAD変換器、それを用いた受信機及び無線通信システム,” ,特願2014-181162, 出願日:平成26年9月5日.

- 牟田 修, 古川 浩, 兼本大輔, 小寺康平, “量子化雑音の影響下の定包絡線変調システムにおける非線形等化技術,” 特願2012-187912, 出願日:平成24年8月28日.

- 上野武司, 兼本大輔, “連続時間ΔΣ変調器,” 特願2006-320206, 出願日:平成18年11月28日.

H. セミナー Seminar

- ”ディジタル信号処理の基礎とディジタルフィルタの設計のポイントおよび雑音除去技術と圧縮センシングへの応用”

日本テクノセンター オンラインセミナー, 2025年 1月27日

発表者:兼本大輔

- ”アナログ回路設計の基礎とその実践ポイントおよび最新技術”

日本テクノセンター オンラインセミナー, 2024年 7月16日

発表者:兼本大輔

- ”ディジタル信号処理・ディジタルフィルタの基礎と効果的なノイズ除去処理技術への応用 〜デモ付〜 <オンラインセミナー> ”

日本テクノセンター オンラインセミナー, 2024年 1月16日

発表者:兼本大輔

- ”生体信号計測の基礎と生体計測回路システムの設計および応用”

日本テクノセンター オンラインセミナー, 2023年 6月16日

発表者:兼本大輔

- "Recent studies about Delta-Sigma Modulators"

Analog Devices, Inc.(Toronto), Oct,2013

Daisuke Kanemoto

- "パワーエレクトロニクスの為のDigital-to-Analog Converter設計事例"

長崎大学 2012年5月

発表者: 兼本大輔

- "データコンバータLSIの基礎"

長崎大学 プロジェクト実験 2011年10月

発表者: 兼本大輔

- "高精度・低消費電力デルタシグマ変調器の設計" (企業内講演)

アナログ・デバイセズ(株) 東京デザインセンター 2011年9月

発表者: 兼本大輔

- "オペアンプシェアリング技術を活用したデルタシグマ変調器の設計" (企業内講演)

(株)東芝 研究開発センター ワイヤレスシステムラボラトリー 2011年9月

発表者: 兼本大輔

I. 記事 Article

- Daisuke Kanemoto

"Technical Note--Slowdown in the Energy Efficiency of Analog-to-Digital Converters and a Compressed-Sensing-Based Solution,"

OUKA, June, 30, 2025, pp.1-4

- 兼本大輔

"圧縮センシングを用いた省電力無線センサーシステム バッテリーレスセンシングへの挑戦"

クリーンテクノロジー, 日本工業出版, 2025年2月号, pp.54-59

- 兼本大輔

"圧縮センシングを活用した無線脳波計測デバイス実現に向けた研究"

「光学」2023年10月号 フォーカス記事, vol. 52, 2023年10月, pp.439-441

- 兼本大輔

"LSI設計に関する業績に対して「第20回山梨科学アカデミー奨励賞」を受賞"

山梨工業会会報(第120号), 2015年

- 兼本大輔

"様々な分野に応用出来る集積回路設計の考え方"

電子情報通信学会 会誌平成27年1月号特別小特集, 2015年 1月号 pp.31

- 兼本大輔

"電気学会・電子情報通信学会・IEEEよりLSI設計に関する3件の賞を受賞"

山梨工業会会報(第118号), 2014年 9月号

- 兼本大輔

"LSIおよび他分野でも活用できるアナログ集積回路設計の考え方"

電気学会誌, 2014年 5月号 pp.283

- 金谷晴一,兼本大輔,ポカレルラメシュ, 吉田啓二

"超小型平面アンテナ一体型送受信回路の開発"

OHM, オーム社, 2012年 4月号 pp.6-7

J. 招待講演 Invited Lecture

- 発表者:兼本大輔

タイトル:"ハード・ソフトの融合で切り拓く省電力・バッテリーレスセンシング ─ 圧縮センシングによるアプローチ ─"

イベント名:DAシンポジウム2025 -システムとLSIの設計技術-

主催:情報処理学会 システムとLSIの設計技術研究会(SLDM)

発表日:2025年8月28日(ゆのくに天祥(石川県加賀市))

資料:概要

- 発表者:兼本大輔

タイトル:"「電源問題」に挑む次世代センシング技術〜圧縮センシングで目指すバッテリーレス動作の実現に向けて〜"

イベント名:テクトロ二クス・イノベーション・カンファレンス2025

主催:Tektronix

開催日:2025年7月3日@ステーションコンファレンス東京 (サピアタワー5F)

資料:リーフレット

発表資料(公開予定)

- 発表者:兼本大輔

タイトル:"圧縮センシングを活用した省電力センシングシステム 〜僅かな温度差で動作するバッテリーレス無線脳波伝送システムの紹介〜"

イベント名: 2025年 第1回長崎大学ヘルステック未来創造研究会

主催:長崎大学

開催日:2025年2月7日@長崎スタジアムシティ(NUTIC)講義室2

- 発表者:兼本大輔

タイトル:"ハードウェア・ソフトウェア協調設計による高精度省電力生体信号センシング技術"

イベント名: 第9回 ライフサイエンス・セミナー

主催:パナソニックホールディングス株式会社 技術企画室 オープンイノベーション推進部、パナソニック基盤協働研究所

開催日:2023年11月1日@パナソニックホールディングス株式会社 西門真構内 EXラボ + オンライン

資料:リーフレット

- 発表者:兼本大輔

タイトル:"ハードウエア・ソフトウエアの協調設計による「超低消費電力(バッテリーレス)・高精度センサシステム」の創造"

イベント名:OU×OSTEC「世界を変える最先端テクノロジーセミナー 〜社会実装の共創パートナー探索〜」

主催:大阪大学大学院工学研究科×大阪科学技術センター

開催日:2023年9月11日@大阪大学吹田キャンパス

資料:リーフレット

- 発表者:兼本大輔

タイトル:"圧縮センシングを活用した脳波計測システム"

イベント名:基礎セミナー「バイオセンシング技術の進展」

主催:応用物理学会・東海支部

開催日:2021年10月28日@オンライン

資料:

- 発表者:兼本大輔

タイトル:"実体験から学ぶ国際競争力向上を意識した研究活動の進め方"

イベント名:第25回 アナログVLSIシンポジウム

主催:電気学会・電子回路研究専門委員会

開催日:2021年5月14日@オンライン

資料:

- 兼本大輔

"半導体集積回路の動向"

Mt.Fuji Innovation Engine, 2018年 8月

- 兼本大輔

"超低消費電力・超高精度変換を両立する A/D変換LSIに 関する研究"

山梨科学アカデミー奨励賞受賞講演(第20回山梨科学アカデミー奨励賞 記念講演), 2018年 5月

- 兼本大輔

"米国留学を経て"

山梨大学 第17回 アカデミックサロン 2017年7月21日

山梨大学 第17回 アカデミックサロン 2017年7月21日

- 兼本大輔

"オペアンプシェアリング技術を用いたデルタシグマ変調器の一設計法"

電子回路研究会(最優秀論文発表受賞者 記念講演), 2014年 3月

K. マスメディア Mass Media

- 新藤一彦,兼本大輔, 松本拓真

ラジオ FM千里 て) 寺谷一紀の千里の道は世界へ通ず2025年6月13日放送分

- 兼本大輔

【Article】TechXplore

2025年5月28日記事

An energy-efficient, high-precision measurement system using waveform similarity

- 兼本大輔

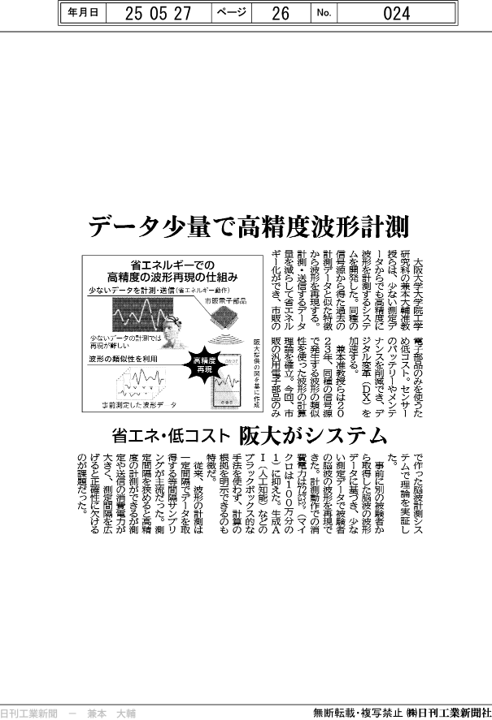

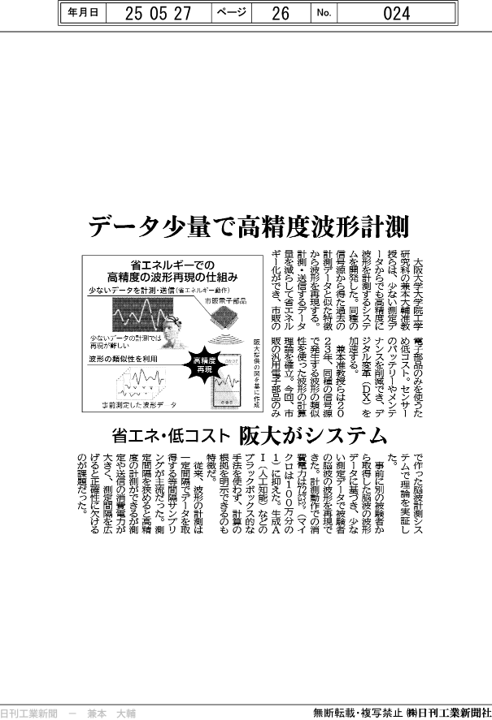

【記事】 日刊工業新聞

2025年5月27日記事

阪大、データ少量で高精度波形計測 省エネ・低コストシステム

- 兼本大輔

【記事】 NIKKEI Tech Foresight

阪大、体温発電で信号処理 ウエアラブル機器を小型化 阪大、体温発電で信号処理 ウエアラブル機器を小型化

- 兼本大輔

【報道】 EE Times Japan, Yahoo! ニュース

センシング回路の消費電力を7割削減 電池レスで、脳波信号の計測と無線伝送を可能に

- 兼本大輔

ラジオ FM Fuji GOOD DAY 「山梨大学FUTURE SEED」 2019年2月28日・3月7日放送分

L. イベント Event

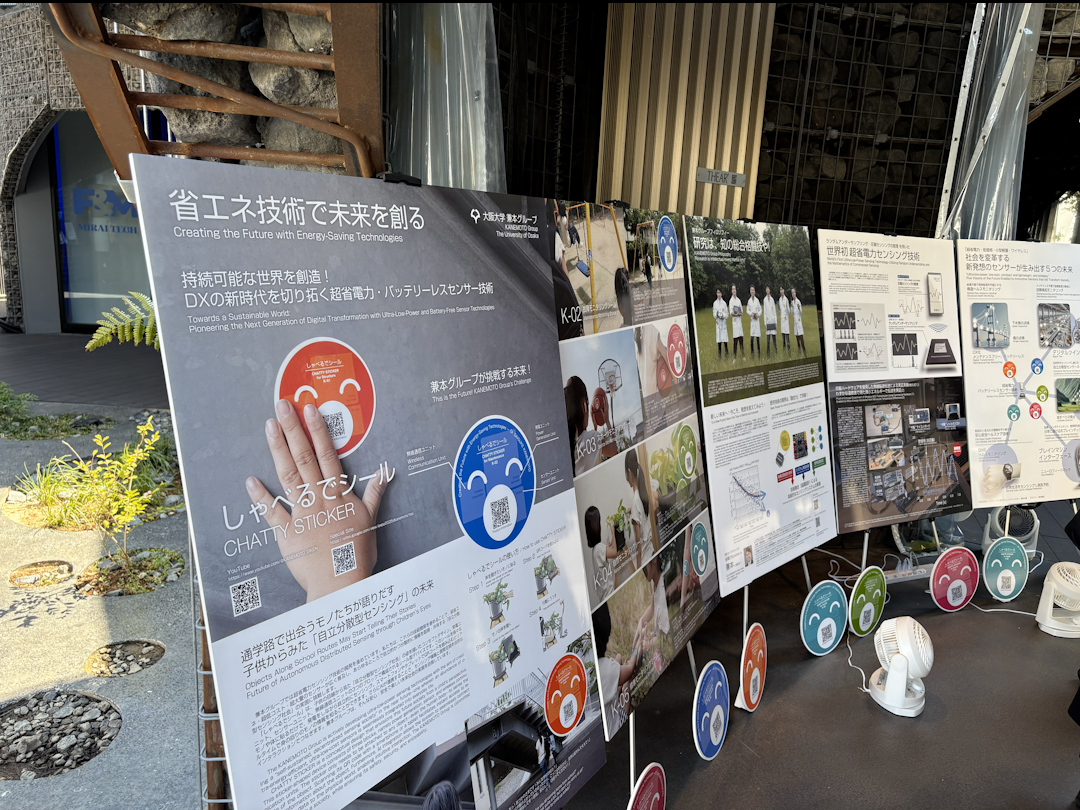

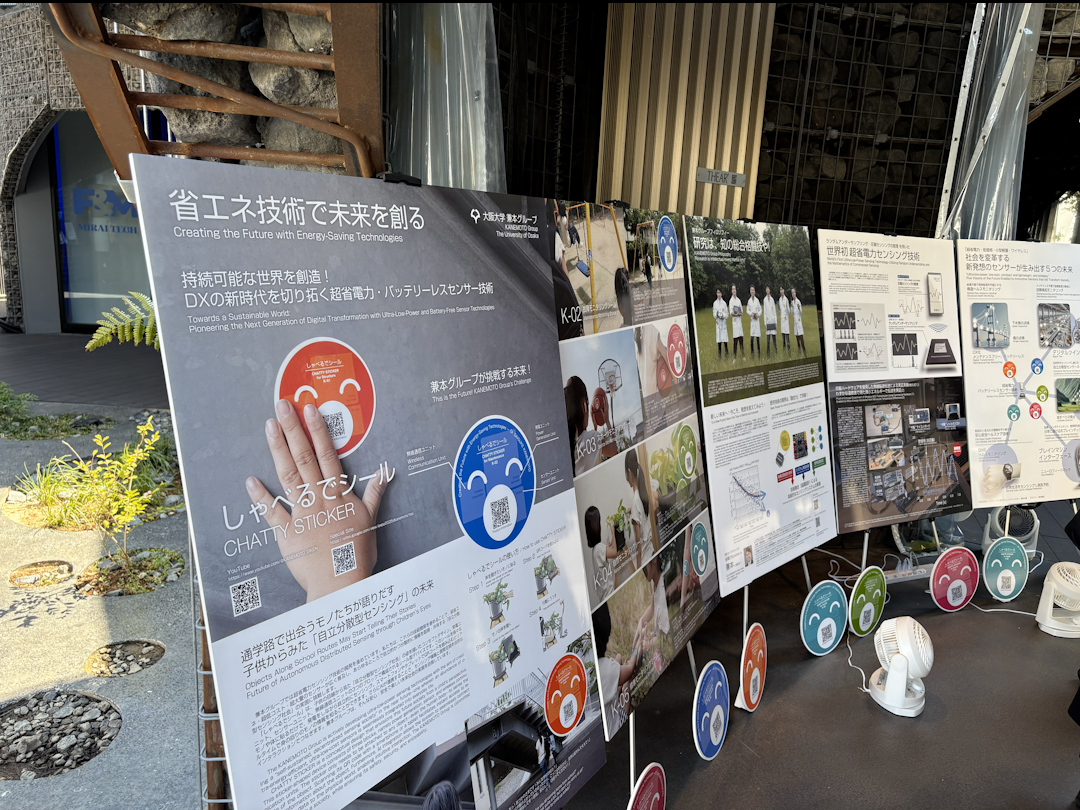

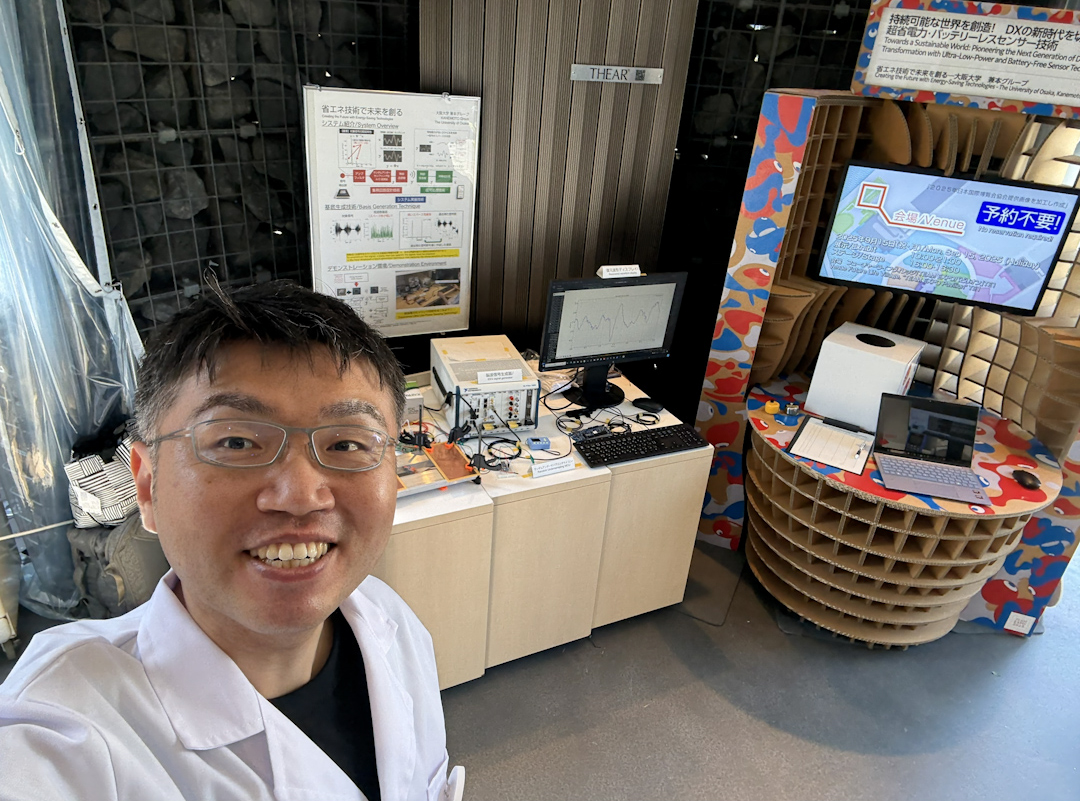

- 「TEAM EXPO 2025 MEETING」/「ATC TEAM EXPO PAVILION」にてデモ展示 @おおさかATCグリーンエコプラザ

TEAM EXPO 祭り「TEAM EXPO 2025 MEETING」(2025年11月21日)

TEAM EXPO 祭り「ATC TEAM EXPO PAVILION」(2025年11月22日)

- 「TEAM EXPOパビリオン」にて展示 @大阪・関西万博 (2025年9月15日)

「省エネ技術で未来を創る 兼本グループ」特設サイト

当日展示の様子

Top

Last update: 2025/12/17

山梨大学 第17回 アカデミックサロン 2017年7月21日

山梨大学 第17回 アカデミックサロン 2017年7月21日